絕緣體上矽,在整個行業向新一代半導體器件的衍變過程中,晶片製造商面臨著嚴峻的挑戰。具體的講,生產高性能晶片的製造商面臨的挑戰來自對速度更快、溫度更低的晶片設計的需求。用於移動套用的晶片製造商需要的是功耗更小的半導體器件。為了應對這些挑戰,大多數業界領先的器件製造商都選擇了絕緣體上矽。

基本介紹

- 中文名:絕緣體上矽

- 實質:新型材料

- 領域:半導體

- 用途:導電

絕緣體上矽,在整個行業向新一代半導體器件的衍變過程中,晶片製造商面臨著嚴峻的挑戰。具體的講,生產高性能晶片的製造商面臨的挑戰來自對速度更快、溫度更低的晶片設計的需求。用於移動套用的晶片製造商需要的是功耗更小的半導體器件。為了應對這些挑戰,大多數業界領先的器件製造商都選擇了絕緣體上矽。

絕緣體上矽,在整個行業向新一代半導體器件的衍變過程中,晶片製造商面臨著嚴峻的挑戰。具體的講,生產高性能晶片的製造商面臨的挑戰來自對速度更快、溫度更低的晶片...

SOI——納米技術時代的高端矽基材料進展,SOI新材料的製備科學,SOI材料與器件特有的物理效應,絕緣體上鍺矽(silicon germanium on insulator, SGOI)新結構和應變矽的...

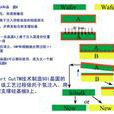

矽基材料是在常規矽材料上製作的,是常規矽材料的發展和延續,其器件工藝與矽工藝相容。主要的矽基材料包括SOI(絕緣體上矽)、GeSi和應力矽。SOI技術已開始在世界上...

矽基材料是在常規矽材料上製作的,是常規矽材料的發展和延續,其器件工藝與矽工藝相容。主要的矽基材料包括SOI(絕緣體上矽)、GeSi和應力矽。目前SOI技術已開始在...

1.專利名稱:一種製備低柵擴展電容絕緣體上矽體接觸器件的方法發明人: 畢津順,海潮和2.專利名稱:一種CMOS積體電路抗單粒子輻照加固電路...

PLC光器件一般在六種材料上製作,它們是:鈮酸鋰(LiNbO3)、Ⅲ-Ⅴ族半導體化合物、二氧化矽(SiO2)、SOI(Silicon-on-Insulator,絕緣體上矽)、聚合物(Polymer)和玻璃...

絕緣體上矽(Silicon On Insulator,SOI)技術作為一種全介質隔離技術,消除了體矽CMOS電路的寄生NPNP通道,具有抗閉鎖效應的能力;在輻射環境中,由於輻射引起的電荷收集...