基本介紹

- 中文名:組合電路

- 外文名:combinational logic circui

- 別名:組合邏輯電路

- 構成:由門電路構成

- 套用:計算機、數字控制、通信

- 對象:離散信號

電路特點

電路設計

電路分析

常見組合電路

編碼器

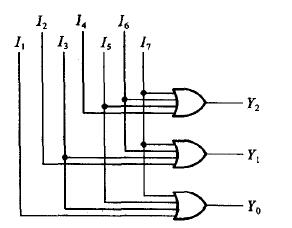

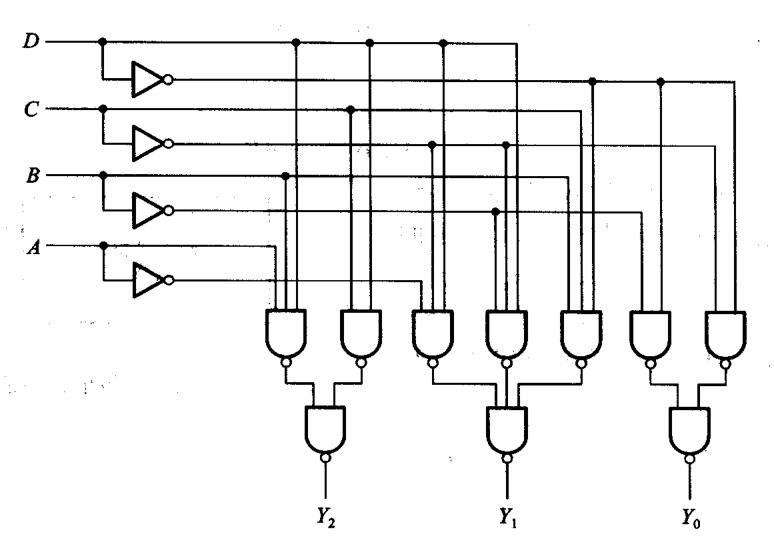

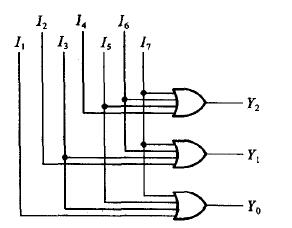

3位二進制編碼器

3位二進制編碼器號。不過在設計優先編碼器時已經將所有的輸人信號按優先順序排了隊,當幾個輸人信號同時出現時,只對其中優先權最高的一個進行編碼。

3位二進制編碼器

3位二進制編碼器數字電路根據邏輯功能的不同特點,可以分成兩大類,一類叫組合邏輯電路(簡稱組合電路),另一類叫做時序邏輯電路(簡稱時序電路)。組合邏輯電路在邏輯功能上的特點是任意...

數字電路根據邏輯功能的不同特點,可以分成兩大類,一類叫組合邏輯電路(簡稱組合電路),另一類叫做時序邏輯電路(簡稱時序電路)。組合邏輯電路在邏輯功能上的特點是任意...

邏輯電路是一種離散信號的傳遞和處理,以二進制為原理、實現數位訊號邏輯運算和操作的電路。分組合邏輯電路和時序邏輯電路。前者由最基本的“與門”電路、“或門”...

雖然每個數字電路系統可能包含有組合電路,但是在實際套用中絕大多數的系統還包括存儲元件,我們將這樣的系統描述為時序電路。時序電路,是由最基本的邏輯門電路加上反饋...

組合原理是指事物的整體或部分迭加的原理。...... 系統組合:是指根據事物之間的聯繫,將它們有機地結合成為一體,具有化零為整的功能。例如,集成電路是以半導體晶體...

555時基電路是一種將模擬功能與邏輯功能巧妙結合在同一矽片上的組合集成電路。...... 555時基電路是一種將模擬功能與邏輯功能巧妙結合在同一矽片上的組合集成電路...

數字電路根據邏輯功能的不同特點,可以分成兩大類,一類叫組合邏輯電路(簡稱組合電路),另一類叫做時序邏輯電路(簡稱時序電路)。組合邏輯電路在邏輯功能上的特點是任意...

電路板的名稱有:陶瓷電路板,氧化鋁陶瓷電路板,氮化鋁陶瓷電路板,線路板,PCB板,鋁基板,高頻板,厚銅板,阻抗板,PCB,超薄線路板,超薄電路板,印刷(銅刻蝕技術)電路...

在數字電路中,所謂“門”就是只能實現基本邏輯關係的電路。最基本的邏輯關係是與、或、非,最基本的邏輯門是與門、或門和非門。邏輯門可以用電阻、電容、二極體、...

乘法電路(multiplying circuit)是一種完成兩個互不相關的模擬信號相乘作用的電子器件。它可以將兩個二進制數相乘。它是由更基本的加法電路組成的。...

為實現能量和信號的傳輸,連線各個功能電路的方法即為耦合電路。一般的,耦合電路通常具有濾波、蓄能、隔離、阻抗變換等一種或幾種功能。...

用以實現基本邏輯運算和複合邏輯運算的單元電路稱為門電路。常用的門電路在邏輯功能上有與門、或門、非門、與非門、或非門、與或非門、異或門等幾種。...

用數位訊號完成對數字量進行算術運算和邏輯運算的電路稱為數字電路,或數字系統。由於它具有邏輯運算和邏輯處理功能,所以又稱數字邏輯電路。現代的數字電路由半導體工藝...

主電路(Power Circuit)是指在電器設備或電力系統中,直接承擔電能的交換或控制任務的電路。在配電櫃中主電路多指高壓迴路,為整個系統以及大功率在執行元件提供動力,...

《圖解電路》是一本由科學出版社在2006年出版的書籍。本書是“零起點電路入門叢書”之一,書中主要講解電路方面的基本知識。...

組合總數(total number of combinations)是一個正整數,指從n個不同元素里每次取出0個,1個,2個,…,n個不同元素的所有組合數的總和,即Cºn+C¹n+C²n...

在各類工業自動控制系統中,有很大一類屬於開關量的自動控制系統,包括繼電接觸控制系統、半導體邏輯控制系統和順序控制系統等。構成這類開關控制系統的基礎是開關電路。...

基因電路是波士頓大學生物醫學工程師科林斯(J.Collins)的研究組在2000年設計了觸發器開關功能的基因電路,研製出一種“套環開關”,所選擇的細胞功能可隨意開關。...

(電信)電路,兩點間兩條傳輸方向相反的(傳輸)通路的組合,以提供雙向傳輸。...... (電信)電路,兩點間兩條傳輸方向相反的(傳輸)通路的組合,以提供雙向傳輸。...

用以實現基本邏輯運算和複合邏輯運算的單元電路稱為門電路。常用的門電路在邏輯功能上有與門、或門、非門、與非門、或非門、與或非門、異或門等幾種。...

“整流電路”(rectifying circuit)是把交流電能轉換為直流電能的電路。大多數整流電路由變壓器、整流主電路和濾波器等組成。它在直流電動機的調速、發電機的勵磁調節...

與非門(英語:NAND gate)是數字電路的一種基本邏輯電路。是與門和非門的疊加,有多個輸入和一個輸出。1若當輸入均為高電平(1),則輸出為低電平(0);若輸入中...

超大規模集成電路(Very Large Scale Integration Circuit,VLSI)是一種將大量電晶體組合到單一晶片的集成電路,其集成度大於大規模集成電路。集成的電晶體數在不同的...

混合集成電路是由半導體集成工藝與薄(厚)膜工藝結合而製成的集成電路。混合集成電路是在基片上用成膜方法製作厚膜或薄膜元件及其互連線,並在同一基片上將分立的...

電流的方向與正電荷在電路中移動的方向相同。實際上並不是正電荷移動,而是負...鉗形表是 由電流互感器和電流表組合而成。電流互感器的鐵心在捏緊扳手時可以...