基本介紹

- 中文名:淺槽隔離

- 外文名: shallow trench isolation, STI

- 適用工藝:半導體工藝

內容簡介:,工藝步驟:,槽刻蝕,氧化物填充,氧化物平坦化,工藝優點:,

內容簡介:

淺槽隔離(Shallow Trench Isolation;STI)技術製作主動區域之間的絕緣結構已逐漸被普遍採用。STI結構的形成通常是先在半導體基底上沉積一層氮化矽層,然後圖案化此氮化矽層形成硬掩膜。接著蝕刻基底,在相鄰的元件之間形成陡峭的溝渠。最後,在溝渠中填入氧化物形成元件隔離結構。雖然STI工藝比LOCOS工藝擁有較佳的隔離特性,然而由於電漿破壞,可產生大量的蝕刻缺陷,且具有尖銳角落的陡峭溝渠也會導致角落寄生漏電流(Corner Parasiticleakage),因而降低STI的隔離特性。

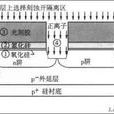

用於亞0.25um工藝的選擇性氧化的主要技術是淺槽隔離(STI)。STI技術中的主要絕緣材料是澱積氧化物。選擇性氧化利用掩模來完成,通常是氮化矽(Si3N4)。掩模經過澱積、圖形化。刻蝕矽後形成槽。在掩模圖形暴露的區域,熱氧化150~200Å厚的氧化層之後,才能蝕矽形成槽(如圖1所示)。這種熱生長的氧化物是矽表面鈍化,並且可以使淺槽填充的澱積氧化物與矽相互隔離。它還能作為有效的阻擋層,避免器件中的側牆漏電流產生。

圖1 STI氧化矽襯層

圖1 STI氧化矽襯層在0.25um和以下的技術節點中,淺槽隔離(STI)技術被廣泛套用。STI取代LOCOS的原因有如下幾點:

(1) 更有效的器件隔離的需要,尤其是對DRAM器件而言;

(2) 對電晶體隔離而言,表面積顯著減小;

(3)超強的閂鎖保護能力;

(4) 對溝道沒有侵蝕;

(5) 與CMP的兼容。

在基本的STI工藝中(如圖2所示),利用乾法刻蝕在矽片表面可以刻出深0.3~0.8um的溝,這些溝有直角和圓角。STI溝的深寬比大約在2:1~5:1,由於DRAM器件對漏電流的敏感,需要更高的深寬比。隔離溝表面生長有線性的氧化層,用CVD氧填充,並利用CMP來平坦化。STI較LOCOS技術成本更高,因為需要更複雜的工藝步驟。然而,STI的優點足以彌補成本高的問題。

圖2 淺層隔離

圖2 淺層隔離工藝步驟:

槽刻蝕

- 隔離氧化層。矽表面生長一層厚度約150埃氧化層;可以做為隔離層保護有源區在去掉氮化物的過程中免受化學沾污。

- 氮化物澱積。矽表面生長一薄層氮化矽:a)由於氮化矽是堅固的掩膜材料,有助於在STI氧化物澱積過程中保護有源區 b)在CMP時充當拋光的阻擋材料。

- 掩膜,淺槽隔離

- STI槽刻蝕。在經過上面的光刻之後把沒有被光刻膠保護的區域用離子和強腐蝕性的化學物質刻蝕掉氮化矽、氧化矽和矽。需要注意的是會在溝槽傾斜的側壁及圓滑的底面有助於提高填充的質量和隔離結構的電學特性

氧化物填充