時鐘信號延滯是指時鐘源插入延遲和時鐘網路插入延遲。

基本介紹

- 中文名:時鐘信號延滯

- 外文名:Clock signal delay

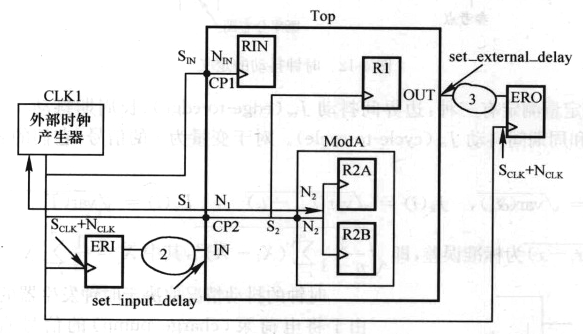

時鐘信號延滯(latency)又被稱為插入延遲(insertion delay),它包括兩部分,即時鐘源(clock source)插入延遲和時鐘網路(clock network)插入延遲。時鐘源插入延遲是來自系統(即時鐘源或來自晶片)到當前晶片(或到當前模組)時鐘根節點(clock root pin)之間的延遲,時鐘網路延遲是時鐘樹的延遲。從時鐘源到時鐘樹暫存器的插入延遲事實上包括了兩者之和(圖1),即總插入延遲。在理想時鐘的情況下,人們假定時鐘網路插入延遲為零。在時鐘樹綜合時,時鐘延滯的數值會直接用來對偏差做計算和固定。

圖1 定義的時鐘插入延遲(Sxx為時鐘源延遲;Nxx為時鐘網路延遲)

圖1 定義的時鐘插入延遲(Sxx為時鐘源延遲;Nxx為時鐘網路延遲)上述兩種延遲的定義可以通過特定的選項加以區分,如:

set_clock_latency 2.0 -source [get_clocks {cpu_clk}]

set_clock_latency 2.0 [get_clocks {cpu_clk}]

前者定義了時鐘源的插入延遲,而後者定義了時鐘網路插入延遲,兩者通過-source選項加以區分。