基本介紹

- 中文名:控制暫存器

- 領域:彙編語言

CR0中協處理器控制位

ET

TS

CR0中的標誌 | 指令類型 | |||

EM | MP | TS | 浮點 | WAIT/FWAIT |

0 | 0 | 0 | 執行 | 執行 |

0 | 0 | 1 | 設備不存在(DNA)異常 | 執行 |

0 | 1 | 0 | 執行 | 執行 |

0 | 1 | 1 | DNA異常 | DNA異常 |

1 | 0 | 0 | DNA異常 | 執行 |

1 | 0 | 1 | DNA異常 | 執行 |

1 | 1 | 0 | DNA異常 | 執行 |

1 | 1 | 1 | DNA異常 | DNA異常 |

CR0中的標誌 | 指令類型 | |||

EM | MP | TS | 浮點 | WAIT/FWAIT |

0 | 0 | 0 | 執行 | 執行 |

0 | 0 | 1 | 設備不存在(DNA)異常 | 執行 |

0 | 1 | 0 | 執行 | 執行 |

0 | 1 | 1 | DNA異常 | DNA異常 |

1 | 0 | 0 | DNA異常 | 執行 |

1 | 0 | 1 | DNA異常 | 執行 |

1 | 1 | 0 | DNA異常 | 執行 |

1 | 1 | 1 | DNA異常 | DNA異常 |

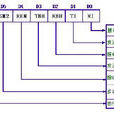

控制暫存器(CR0~CR3)用於控制和確定處理器的操作模式以及當前執行任務的特性,如圖4-3所示。CR0中含有控制處理器操作模式和狀態的系統控制標誌;CR1保留不用;CR2...

暫存器是中央處理器內的組成部分。暫存器是有限存貯容量的高速存貯部件,它們可用來暫存指令、數據和地址。在中央處理器的控制部件中,包含的暫存器有指令暫存器(IR)和...

SCON(Serial Control Register)串列口控制暫存器,用於控制串列通信的方式選擇、接收和傳送,指示串口的狀態。SCON既可以位元組定址,也可以位定址,其位元組地址為98H,地址位...

ie,中斷允許控制暫存器,電工學用語。用於控制所有中斷源的開放或禁止,以及每箇中斷源是否被允許。...

特殊功能暫存器是80C51單片機中各功能部件對應的暫存器,用於存放相應功能部件的控制命令,狀態或數據。...

標誌暫存器又稱程式狀態字(外語縮寫:PSW、外語全稱:Program Status Word)。這是一個16位的存放條件標誌、控制標誌暫存器,主要用於反映處理器的狀態和ALU運算結果的...

狀態暫存器又名條件碼暫存器,它是計算機系統的核心部件——運算器的一部分,狀態暫存器用來存放兩類信息:一類是體現當前指令執行結果的各種狀態信息(條件碼),如有無...

暫存器定址方式,是一種定址方式。...... SI源地址(源變址暫存器)DI目的地址(目的變址暫存器)控制暫存器:IP指令指針FLAG標誌暫存器①進位標誌 CF,記錄運算時最高有效...

在數字電路系統工作過程中,把正在處理的二進制數據或代碼暫時存儲起來的操作叫做暫存,暫存器電路就是實現暫存功能的電路,是數字邏輯電路的基礎模組。...

SCON串列口控制暫存器通常在晶片或設備中為了監視或控制接口狀態,都會引用到接口控制暫存器。SCON 就是51 晶片的串列口控制暫存器。它的定址地址是98H,是一個可以位...

指令指針暫存器IP(X86型CPU)相當於ARM型CPU中的程式計數器PC,用於控制程式中指令的執行順序。正常運行時,IP中含有BIU要取的下一條指令(位元組)的偏移地址,一般情況...

浮點暫存器,80486微處理器的浮點暫存器是由80486處理器晶片集成的浮點處理單元(FPU)來完成的,...

用來保存當前CPU所訪問的記憶體單元的地址。由於在記憶體和CPU之間存在著操作速度上的差別,所以必須使用地址暫存器來保持地址信息,直到記憶體的讀/寫操作完成為止 。 ...

任何VXI匯流排器件,不管其功能如何,都必須有一組配置暫存器,系統通過訪問VME匯流排上PI口的配置暫存器來識別器件的類型、型號、生產廠家、地址空間與所要求的存儲器空間。...

段暫存器是因為對記憶體的分段管理而設定的。計算機需要對記憶體分段,以分配給不同的程式使用(類似於硬碟分頁)。在描述記憶體分段時,需要有如下段的信息:1.段的大小;2...

PCON全稱Power Control Register,即功率控制暫存器。包含SMOD,SMOD0,LVDF,POF,GF1,GF0,PD,IDL等控制位。在通用51單片機中,SMOD,PD,IDL較為常用。SMOD控制定時...

暫存器說明符只能用於說明函式中的變數和函式中的形參,因此不允許將外部變數或靜態變數說明為"register"。register型變數常用於作為循環控制變數,這是使用它的高速特點...

電源管理暫存器PCON是一款新型電源管理暫存器。...... PCON主要是為CHMOS型單片機的電源控制而設定的專用暫存器,單元地址是87H,其結構格式如下:表2 PCON電源管理暫存器...