基本介紹

Core微架構的處理器

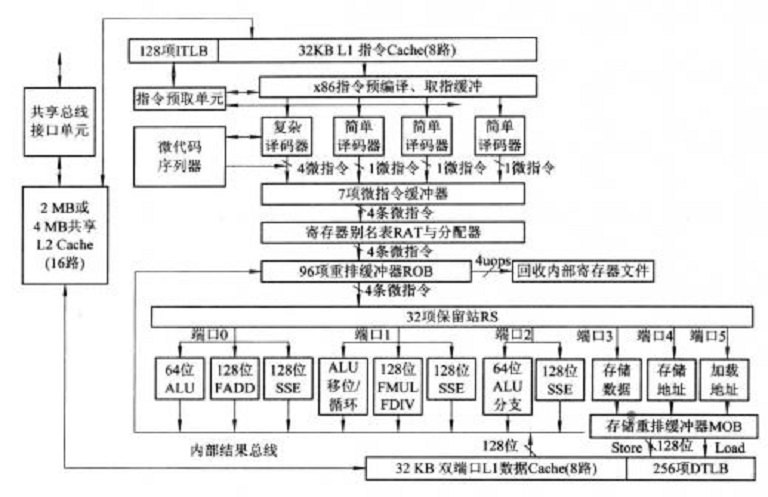

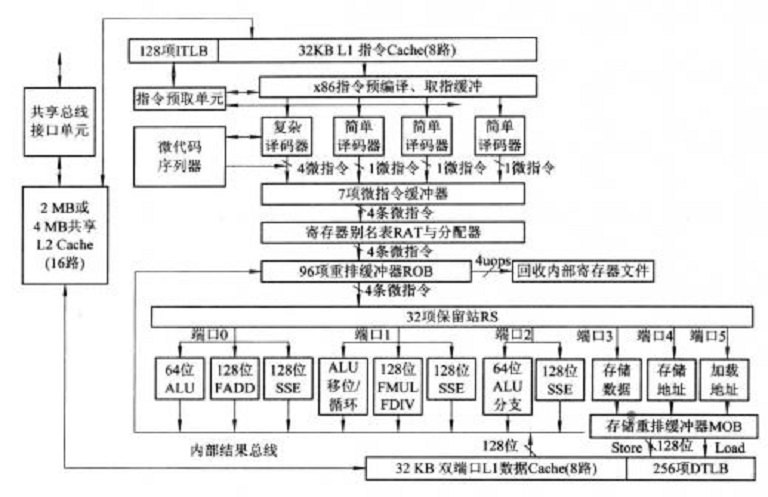

Core微架構處理器的內部結構

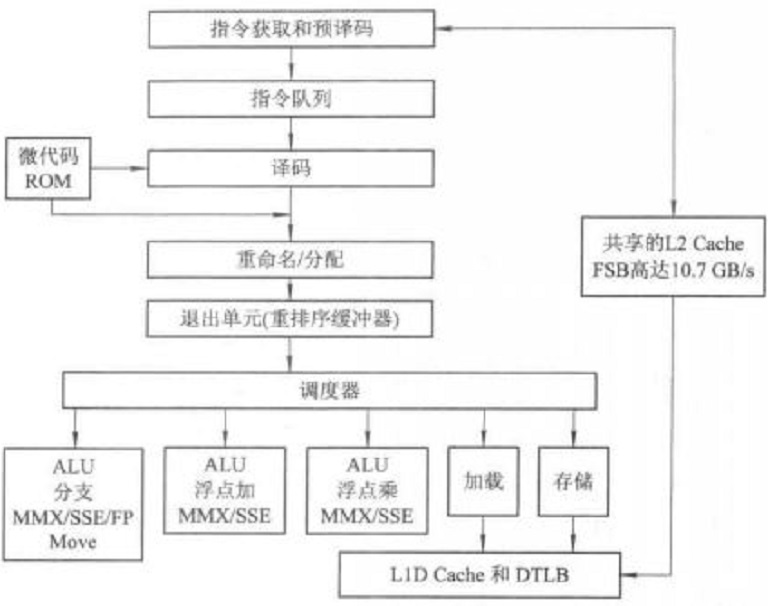

Core微架構處理器的內部結構使用微架構的原因

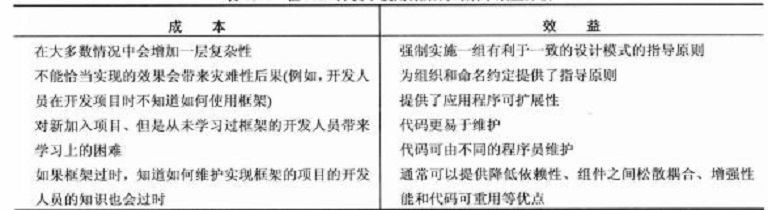

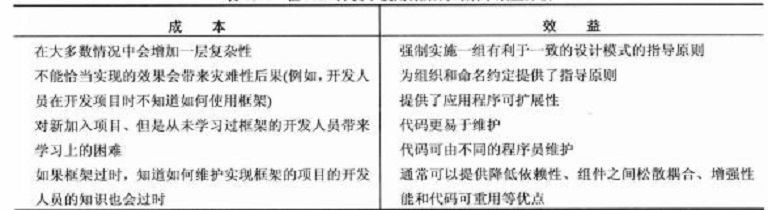

微架構成本分析表

微架構成本分析表Core微架構的優點

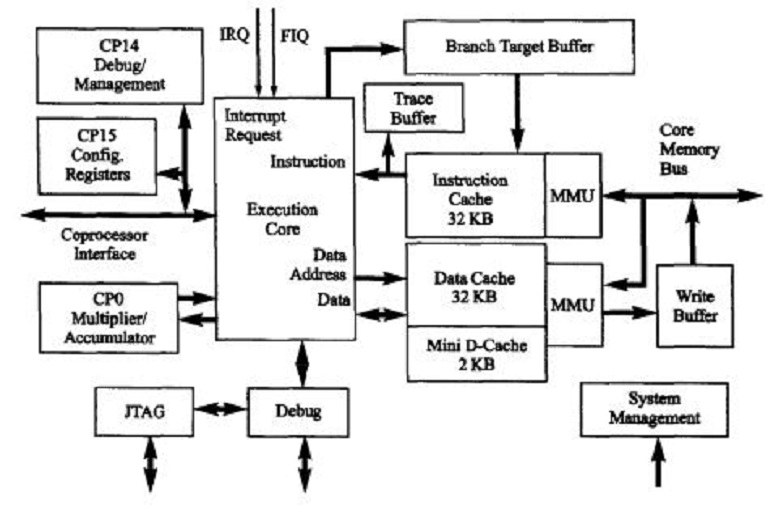

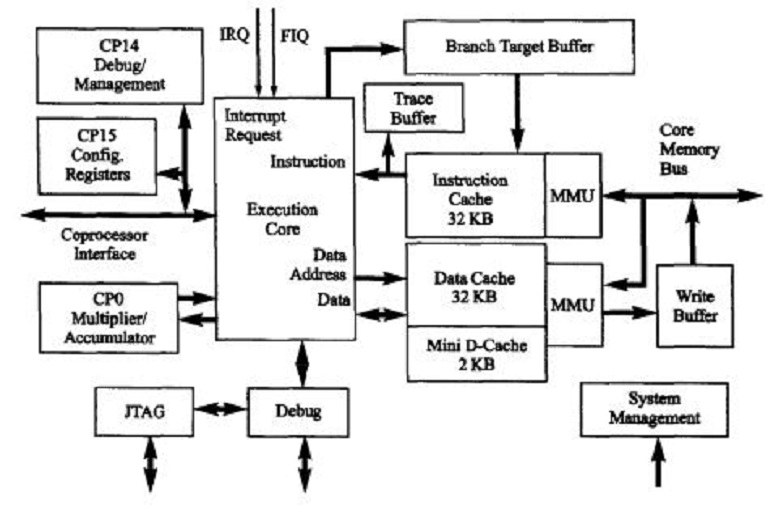

XScale微架構處理器

XScale系統結構圖

XScale系統結構圖

Core微架構處理器的內部結構

Core微架構處理器的內部結構 微架構成本分析表

微架構成本分析表 XScale系統結構圖

XScale系統結構圖微架構又稱為微體系結構/微處理器體系結構。是在計算機工程中,將一種給定的 指令集架構在處理器中執行的方法。一種給定指令集可以在不同的微架構中執行。實施中...

CPU架構是CPU廠商給屬於同一系列的CPU產品定的一個規範,主要目的是為了區分不同類型CPU的重要標示。目前市面上的CPU分類主要分有兩大陣營,一個是intel、AMD為首...

Core微架構(Core Micro-Architecture),通常把“Core ”直接音譯為“酷睿”,Core微架構擁有雙核心、64bit指令集、4發射的超標量體系結構和亂序執行機制等技術,支持...

自1989年起英特爾就一直有條不紊地遵循著其稱為“Tick-Tock模式”的新產品創新節奏,即每隔一年交替推出新一代的先進制程技術和處理器微體系架構,隨著時間的推移,...

伏打((英語:Volta)最早被英偉達宣布在2013年3月的未來路線圖中,是帕斯卡微架構的繼任者。Titan V是最早使用伏打微架構的消費級顯示卡,而專業顯示卡是Tesla V100,例如...

Intel Core(中譯酷睿)是個用來取代Pentium M架構的產品。它是Intel在2006年1月打造新形象時的一部分。第一款晶片的產品代號為Yonah(從希伯來語的Jonah - י...

英特爾酷睿微體系結構是基於英特爾架構的台式、移動式和主流伺服器多核處理器的新基礎。該新微架構擴展了率先在英特爾奔騰M處理器中的英特爾移動微架構上提倡的高能效...

(AMD微處理器架構)編輯 鎖定 AMD開發了代號為“Zen”的全新x86處理器核心,與AMD現有的x86處理器核心相比,每個時鐘周期的指令集可提高40%。 [1] 定製化64位ARM...

Scorpion是高通公司自主設計和研發的第一代處理器微架構,基於ARMv7-A指令集,能夠實現每核最高1.7 GHz的處理速度。...

1.程式設計師可見指令集, 各種微架構的實現2.在ANSI C/C++或者SystemC的體系研究和性能建模3.高級綜合(HLS) 或RTL(例如邏輯) 執行...

Core i7(中文:酷睿i7,核心代號:Bloomfield)處理器是英特爾於2008年推出的64位四核心CPU,沿用x86-64指令集,並以Intel Nehalem微架構為基礎,取代Intel Core 2系列...

實際上,我們把Core音譯為酷睿,它是Intel下一代處理器產品將統一採用的微架構,而Conroe只是對基於Core微架構的Intel下一代桌面平台級產品的代號。除Conroe處理器之外...

Pentium(奔騰)是英特爾第五代x86架構的微處理器,於1993年3月22日開始出貨,是486產品線的後代。Pentium本應命名為80586或 i586,後來命名為“Pentium”(通常認為“...

英特爾酷睿微體系結構是基於新型英特爾架構的台式機、筆記本電腦和主流伺服器多核處理器的基礎。英特爾酷睿微體系架構擁有一流的性能和多種創新特性,且針對多核進行了...

第6階段(2005年至今)是酷睿(core)系列微處理器時代,通常稱為第6代。“酷睿”是一款領先節能的新型微架構,設計的出發點是提供卓然出眾的性能和能效,提高每瓦特...

Intel Skylake是英特爾第六代微處理器架構,採用14納米製程,是Intel Haswell微架構及其製程改進版Intel Broadwell微架構的繼任者。Intel Skylake已經在2015年8月5日20...

微型計算機簡稱“微型機”、“微機”,由於其具備人腦的某些功能,所以也稱其為“微電腦”。微型計算機是由大規模積體電路組成的、體積較小的電子計算機。它是以微...

簡單說來,Nehalem還是基本建立在Core微架構(Core Microarchitecture)的骨架上,外加增添了SMT、3層快取、TLB和分支預測的等級化、IMC、QPI和支持DDR3等技術。中文...