多孔性矽氧化隔離(isolation by oxidized porous silicon)簡稱IOPS,是用多孔性處理和熱氧化兩項工藝在矽表面上形成電絕緣層的方法。這種方法克服了平面法、局部氧化隔離和空氣隔離等方法在工藝上的困難,其特點是不需要高溫或長時間的熱處理就能形成較厚的絕緣層。

基本介紹

- 中文名:多孔性矽氧化隔離

- 外文名:isolation by oxidized porous silicon

- 簡稱:IOPS

- 工藝:多孔性處理和熱氧化

- 特點:不需要高溫或長時間的熱處理

- 學科:電子工程

技術背景,工藝流程,發展趨勢,適用,

技術背景

積體電路中最常使用的隔離技術仍是PN結隔離。這種方法是利用反向偏壓PN結來實現元件之間的隔離,雖 然它是用通常雜質擴散技術就容易完成的方法,但是這種方法對積體電路的超高速化,超集成化具有相當致命的缺點。

PN結電容在高速領域已成為不可忽視的雜散電容,它限制了積體電路的工作速度,同時,由於隔離擴散時 橫向擴展同縱向擴展程度相同,因此 , 為 了從 耐壓 等其它關係 方面考慮隔離擴 散層 同形 成元件的擴散層(例如埋層、收集極補償擴散層、基極擴散層等)之間必須有一定程度的間隔,所以在提高集成度方面也受到了限制。

工藝流程

多孔性矽氧化隔離是將矽片在氟化氫溶液中進行陽極處理,採用適當的電流密度,則矽表面即形成所謂多孔性矽層。多孔性矽層具有非常容易氧化的特性,因此,有選擇地使作隔離部分用的矽具有多孔性,然後在濕氧中進行熱氧化。多孔性矽氧化為厚絕緣層所需的時間比直接使矽氧化的時間大為縮短。

發展趨勢

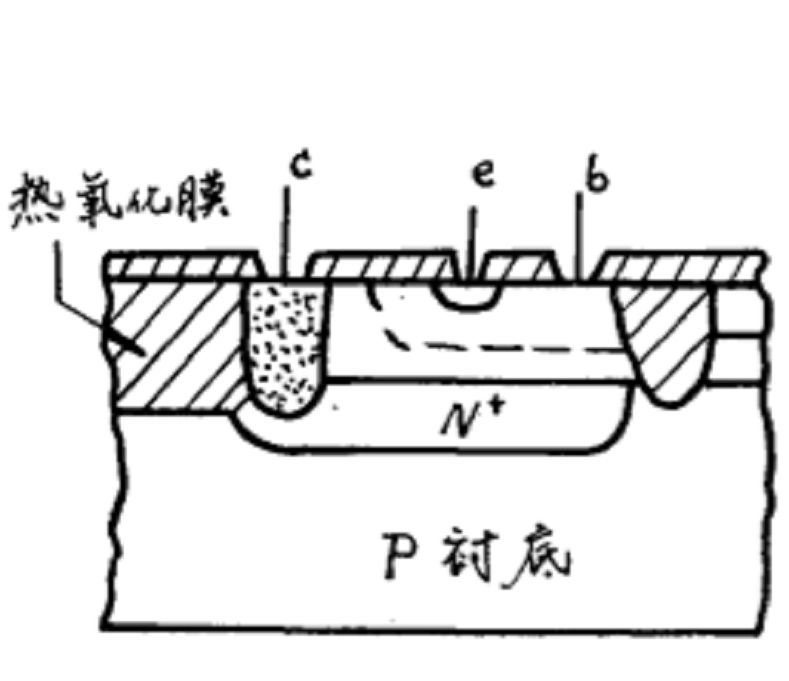

用IPOS技術試製了超高速雙極邏輯電路一有射極跟隨器兩極無閡值邏輯門電路。這個門電路中的電晶體,其發射極用砷、基極由硼摻雜氧化膜法擴收製成。基區寬度為0.15微米,電阻是利用基極補償擴散的擴散電阻。布線電極使用了Al-Ni-Au三層結構(所謂TAMS電極)。隔離區多孔化工藝使用了P-型法。各元件同隔離區的間隔仍很寬,但這同PN結隔離情況不同,使用IPOS技術這個較寬的間隔本來是不必要的,但這樣做可有效地減小由於隔離區同元件接觸而寄生於元件上的雜散電容(例如基區側面電容)。

測定工作速度結果表明,可以得平均每門傳遞延遲時間為0.3毫微秒,速度極高。因此,可以認為,將IPOS技術用於超高速積體電路具有光明的前景。 IPOS技術不僅可用於雙極積體電路,也可適用於MOS積體電路以及各種個別半導體器件,還可作為在半導體村底中埋入絕緣層的技術等等。

適用

多孔性矽氧化隔離方法不僅適用於雙極積體電路,對於MOS積體電路和其它各種分立半導體器件也能適用。