基本介紹

- 中文名:全耗盡型SOI

- 外文名:Fully Depleted Silicon On Insulator, FD-SOI

通常根據在絕緣體上的矽膜厚度將SOI分成薄膜全耗盡FD(Fully Depleted)結構和厚膜部分耗盡PD(Partially Depleted)結構。FD型與PD型相比,由於具有良好的等比例縮小特性,近於理想的亞閾擺幅,高跨導以及浮體效應較小等突出優點,在高速、低壓、低功耗模擬電路、數模混合電路等套用方面受到了人們的特別重視。

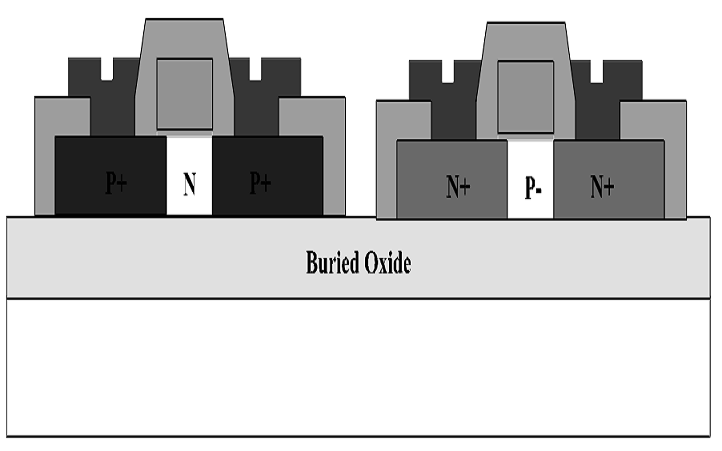

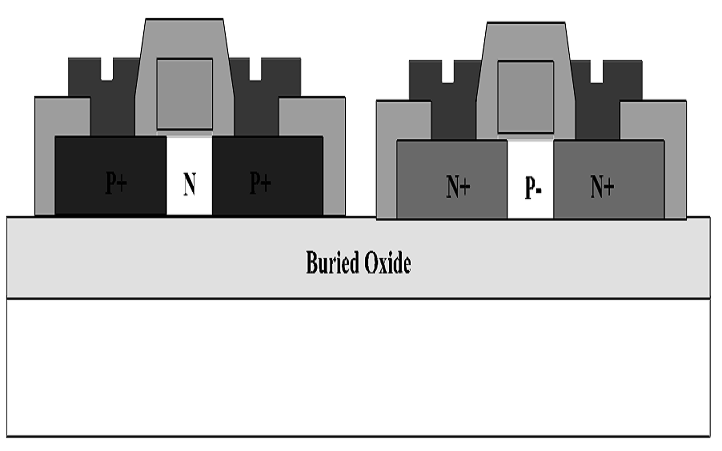

圖1 SOI CMOS器件的橫截面示意圖

圖1 SOI CMOS器件的橫截面示意圖