用軟體實現並行計算機系統的時鐘同步

提出了利用軟體同步實現TANSPUTER系統中各處理器時鐘同步方法。首先對並行計算機系統的時鐘同步問題進行了介紹;然後對一種多處理器的同步算法簡單地進行了描述,並給出了在990一 STAR並行計算機系統中實現的方法;提供了部分程式代碼和註解以及在990一STAR並行計算機系統中獲取的結果;討論了代碼的實用性和可移植性。

同步問題

系統就被認為同步,這可以通過相應的硬體和軟體技術來實現。 討論非容錯的軟體同步方法,其同步思想就是通過並行計算機系統中節點網際網路中的信息交換來計算同步硬體時鐘時所需的調整值。具體實現過程就是假定處理節點中某個處理器的時鐘作為參考時鐘(主時鐘),然後使並行計算機系統中其它的時鐘值與其保持一致,這種機制可通過周期地廣播主時間、並設定從時鐘的值與它接收到的時間值相等來實現。

在系統軟體設計時,因為時間管理總是屬於最高優先權別的進程,系統總是會立即回響時間管理進程,這樣不管Sender和Receiver進程誰先激活,其間的延遲可以用一些常數單位rdmin(最小激活延遲單位)來度量,雖然不知準確的激活延遲為多少,但可以通過將首先激活的進程人為延遲rdmin來得到部分補償。

算法實現和程式結構

算法利用並行C語言和TRANSPUTER彙編語言混合編寫、並已在研製的990一STAR並行計算機系統上側試通過,990一STAR為鬆散藕合的並行計算機系統,包括16個數據處理節點和一個專用圖像處理節點,每個數據處理節點由TRANSPUTER T805和Intel i860通過存貯共享藕合而成,每個i86。具有強大的計算能力,主要完成大負荷的計算。各節點之間的通訊通過T805及其通訊鏈來實現。為了便於系統的擴展和降低硬體的複雜性,整個系統沒有設定硬體全局時鐘,各節點之間的同步採用軟體時鐘來實現。 在TRANSPUTER系統中,LINK不能為幾個同時被激活的進程共享,所以通信不會因LINK的吞吐量而受影響,對於進程激活延遲只要在首先激活的進程中加入適當的記rdmin即可,因為對於以LINK直接連線的節點,數據交換時,總是sender先於Rceciver結束,而對於以C004相連線的節點,情況就不一樣。總之,通過在Master或Slaver同步代碼中插入適當的延時就能補償激活延遲誤差。

程式的核心部分為相鄰PE之間同步延遲的估算,這部分任務由進程send_time和receive_time來完成,receive_time進程還需進行漂移誤差補償,然後設定時鐘值,在這兩進程中還要考慮由於激活順序差異而需補償的時延值rdmin,rdmin加在哪一進程中完全視硬體連線方式而定。

程式基本結構的進程slaver被放在每一個從節點上,進程master放在主節點上,master進程控制廣播時鐘的間隔時間並廣播時鐘,slaver進程負責從選中的通路中接收時鐘值,這步工作通過調用receive_time進程完成,並向指定的連線通路中傳播時鐘值,這步工作通過send_time進程來完成,進程slaver中BOOL變數sync_flag用來標明接收通路和傳送通路,其值由link_inPut過程來完成設定,BOOL型函式sel_sync用來確定與某PE相連的LINK中哪些可用來作同步信號的傳輸。master進程的結構與lslaver進程非常相似,只是不用接收外部的時鐘信號。

運行試驗結果

在990一STAR並行計算機系統上進行了程式調試和運行試驗,990一STAR並行機系統由基於TRANSPUTER通信的17個節點(PE)構成,所以只能獲得d<≈16的試驗結果。在試驗中發現eδ≤1μs,也就是說相鄰兩節點間初始同步誤差在1滴噠內(tick),這樣爭對假設漂移誤差和同步激活最大誤差中的初始同步誤差上限在dμs內,實際的ei0遠比它的上限小,對d ~16的情況做了1000次試驗,其分布情況對16個從PE上作四輪同步操作,每一輪間隙10s所得的最大漂移誤差的分布情況,這些表明採用線性漂移補償導致的漂移誤差eid(t)可以忽略。 ei的一組典型值顯示了總的同步誤差情況,可以看到在d一61的系統中誤差範圍在0一3μs之間。由程式結構可知 , ,在每一輪同步過程中,相鄰節點間的通信量為(21)Byte同步信號和4Byte的時鐘值,通信開銷和用戶程式所需的通信量相比可以忽略,採用這種方法同步時通信所占的系統開銷量極小。

容錯機制的並行計算機系統中同步策略

針對基於容錯的並行計算機系統的高可靠性和高效性的要求,探討了多機系統中較難解決的同步策略。從系統上電同步、任務調度同步和表決同步三個方面提出了容錯與並行處理系統的同步方案,並在樣機上實現。

系統結構

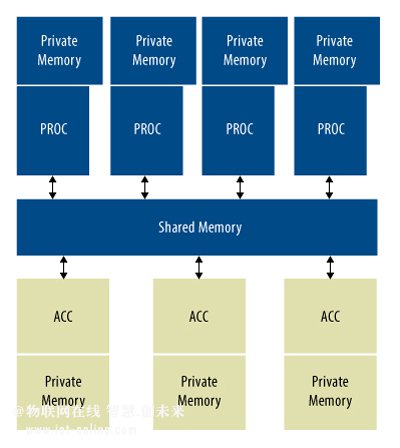

系統採用三模冗餘結構,每個模組主要由計算機、存儲器和匯流排接口單元BIU(Bus Interface Unit)構成。模組內部的存儲器僅供模組中的計算機使用,SM為系統共享存儲器,它供整個系統存放信息及其表格參數,整個系統構成了一個緊藕合的多機系統。匯流排接口單元BIU是模組與系統匯流排之間的瓶頸,每個模組都是通過BIU掛接於匯流排。BIU具有離匯流排與模組的作用,由於三個模組共用一條匯流排,在某一時刻只能有一個模組使用匯流排,通過BIU的內部機制,可以完成模組對匯流排的打開與封鎖,對數據進出匯流排起到控制作用,從而隔離模組與匯流排。另外通過BIU還可以將故障的模組隔離,進行系統重構。系統設計的另一特色是採用了並行匯流排(BUS)和串列匯流排(SBUS)兼有的雙匯流排結構。SBUS連線各CPU的串口,並行匯流排具有匯流排控制(BC)權模組,且持有令牌,令牌在各模組之間的傳遞是通過SBUS完成 。

系統軟體

系統主要是由軟體實現容錯和並行調度管理。系統軟體是一個多機容錯與並行處理的作業系統 , 它負責系統的任務調度、通信機制、同步機制與執行過程的控制和管理。在同步策略模組中實現三模表決與並行處理以及發生故障時的降級重構。系統的同步策略、冗餘管理與並行調度是系統的核心工作。

同步策略

對於多機系統同步是必須要解決的問題,同步策略的優劣直接關係到整個系統多機之間的協調工作、資源分配才不會產生衝突。根據系統的自身特點,把同步策略分為系統上電同步、任務調度同步和表決同步三個方面來考慮。

1、上電同步策略:在常規的多機系統中,每個模組都加入一個時鐘電路。雖然模組內部能做到同步,但在各模組間時鐘誤差累積到一定程度後,就會使系統處於崩潰。系統中只採用一個時鐘電路,這樣系統一開機上電便處於同步狀態。開機上電後各模組開始進行各自的初始化。A模組首先具有BC匯流排控制權,它向其它兩模組發同步信號,然後三個模組根據任務調度算法調度相同的任務進行容錯處理,系統便開始處於任務級同步。

2、任務調度而產生的同步策略:在進行任務劃分時,根據所完成任務的特點和解決方法,將它們事先做容錯和並行劃分,使系統在運行過程中被合理地調度。當從容錯狀態切換到並行工作狀態時,不需要多機之間的協調,各機可直接調用並行處理任務。

從並行到容錯狀態切換採用等待完成調度算法(即先完成的處理機等待其它處理機完成並行任務,然後再調度一個任務進行多機仿作), 具體同步處理過程描述算法如下:

void synchroni Zation(void){

while(本機工作正常){

if(有工作尚未完成){

繼續處理本機工作;}

else{

向其它模組發完成信號;};

if(本機具有BC權){

if(有模組提出升級申請){

調用測試程式檢查其正確性;

if(模組正確)

系統升級;

}

do{waiting;}

until(其它模組的完成信號到);

if(上一任務為並行處理任務){

根據任務調度算法選擇一容錯任務;

向其它模組發容錯處理信號並將任務號一起傳出);

執行這個任務進行容錯處理}。

else{向其它模組發並行處理信號;

根據任務調度算法選擇一併行任務;

執行這個任務;

}

else{

do{waiting;}

until(具有BC權的模組發來下一步處理信號);

if(下一步為容錯處理){

提取該任務號;

調度並執行該任務;

}

eles{根據任務調度算法選擇一任務;

執行該任務;

};

};/*while*/

}

3、同步表決策略:同其它的容錯計算機系統一樣,在完成容錯任務後要對三機運行結果進行大數表決,以此來減小系統運行出錯的機率,提高系統的可靠性。在每次表決之前,先完成的模組要等待後完成的模組,這在一定程度上可減小模組間的異步。系統的同步表決策略與其餘的容錯計算機系統基本相同,但是 ,由於它是一套特殊的容錯系統,在運行的過程中混有並行處理機制,因此在出錯誤後的解決方案就截然不同。