數字電路中,數字電平從高電平(數字“1”)變為低電平(數字“0”)的那一瞬間叫作下降沿。下降沿觸發是當信號有下降沿時的開關動作,當電位由高變低而觸發輸出變化的就叫下降沿觸發。也就是當測到的信號電位是從高到低也就是下降時就觸發,叫做下降沿觸發。

基本介紹

- 中文名:下降沿觸發

- 外文名:falling edge trigger

- 類型:邊沿觸發

- 反義詞:下降沿觸發

基本解釋

硬體描述語言

套用示例

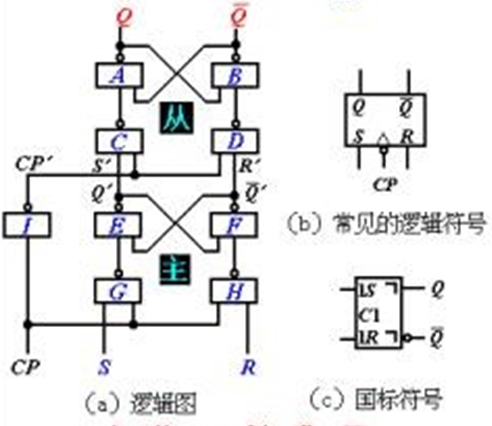

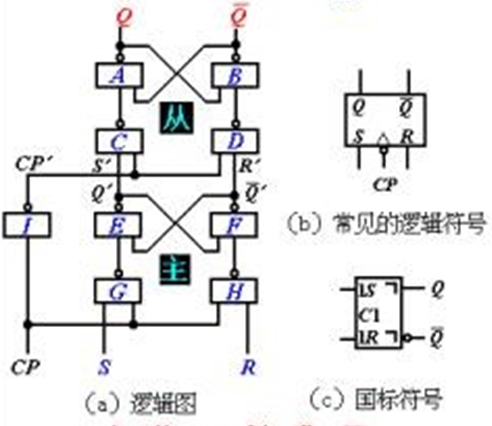

主從RS觸發器

主從RS觸發器數字電路中,數字電平從高電平(數字“1”)變為低電平(數字“0”)的那一瞬間叫作下降沿。下降沿觸發是當信號有下降沿時的開關動作,當電位由高變低而觸發輸出變化的就叫下降沿觸發。也就是當測到的信號電位是從高到低也就是下降時就觸發,叫做下降沿觸發。

主從RS觸發器

主從RS觸發器數字電路中,數字電平從高電平(數字“1”)變為低電平(數字“0”)的那一瞬間叫作下降沿。下降沿觸發是當信號有下降沿時的開關動作,當電位由高變低而觸發輸出...

數字電路中,數字電平從高電平(數字“1”)變為低電平(數字“0”)的那一瞬間叫作下降沿。...

數字電路中,數字電平從低電平(數字“0”)變為高電平(數字“1”)的那一瞬間叫作上升沿。上升沿觸發是當信號有上升沿時的開關動作,當電位由低變高而觸發輸出...

邊沿觸發器,指的是接收時鐘脈衝CP 的某一約定跳變(正跳變或負跳變)來到時的輸入數據。在CP=1及CP=0 期間以及CP非約定跳變到來時,觸發器不接收數據的觸發器...

當輸人端(S、R)狀態發生變化.同時只有時鐘信號輸人端有方波信號時,同步RS觸發器狀態才會發生改變。即在時鐘脈衝下降沿時,觸發器才會按照輸入狀態改變輸出狀態,反...

觸發器暫存器是邊沿敏感的存儲單元,數據存儲的動作有某一信號的上升或者下降沿進行同步的,觸發器的Q輸出端在每一個時鐘沿都會被更新,而所存器只能在使能電平有效...

邊沿D觸發器也稱為維持-阻塞邊沿D觸發器。邊沿D觸發器可由兩個D觸發器串聯而成,但第一個D觸發器的CP需要用非門反向。D觸發器工作原理 編輯 SD和RD接至基本RS...

2、與雙穩態觸發器和單穩態觸發器不同,斯密特觸發器屬於“電平觸發型”電路,不依賴於邊沿陡峭的脈衝。斯密特觸發器套用 編輯 施斯密特觸發器在開環配置中常用於抗...

這樣實現的三分頻占空比為1/3或2/3.如果要實現占空比為50%的三分頻時鐘,可通過待分頻的時鐘上升沿觸發計數器和下降沿觸發計數器進行三分頻,然後將上升沿和下降沿...

K1~K8可以分別觸發與其對應的聲音(低有效),在燒錄晶片的時候,可以設定為下降沿觸發或者低電平觸發等多種觸發模式。K1~K8連線埠有內置上拉電阻,並有防抖動設計,可...

該器件在工作是應在Cext和 Rext/Cext端間外接電容C, Rext/cext和 VDD端間外接電阻R,每個觸發器具有上升沿觸發輸入(TR+)和下降沿觸發輸入(TR-),不用的TR...

這種晶片包括16個引腳,其中四個555定時器共用供電、接地和復位的引腳。放電引腳與閾值引腳被合為同一個引腳並被稱為“定時”。同時觸發引腳改為下降沿觸發。...

時鐘邊沿觸發信號意味著所有的狀態變化都發生在時鐘邊沿到來時刻。只有當同步信號到達時,相關的觸發器才會按輸入信號改變輸出狀態,使得相關的電子組件得以同步運作。...

1,外部中斷源(下降沿觸發) 2,與IOB4組成一個RC反饋電路,以獲得振盪信號,作為外部中斷源EXT1 1,IOB2 設為輸入狀態 2,設定IOB2為反相輸出方式 I/OB3 1,...

外部中斷(EXternal INTerrupt),暫存器可用設定請求輸入模式:1低電平觸發,高電平觸發,上升沿觸發,下降沿觸發或是邊沿觸發. ...

為了克服空翻現象,設計了時鐘觸發器的其他兩種結構:維持阻塞型和邊沿JK觸發器。(1)維持阻塞D觸發器的電路如圖所示。從電路的結構可以看出,它是在基本RS觸發器的...

集成單穩態電路常設有若干個觸發輸入端,包括正邊沿觸發端及負邊沿觸發端。某些電路的內部還附加了一個施密特觸發器,用以改善輸入觸發脈衝的邊沿。此外,還常設有置...

CC4027屬於CMOS邊沿JK觸發器。雙列16腳封裝,雙上升沿J-K觸發器,金屬-氧化物-半導體型互補MOS,電源電壓=3~18V。...

保持時間是指觸發器的時鐘信號上升沿到來以後,數據穩定不變的時間(數據保持不變以便能夠穩定讀取)。...