RGMII(Reduced Gigabit Media Independent Interface)是Reduced GMII(吉比特介質獨立接口)。RGMII均採用4位數據接口,工作時鐘125MHz,並且在上升沿和下降沿同時傳輸數據,因此傳輸速率可達1000Mbps。

基本介紹

- 中文名:精簡吉比特介質獨立接口

- 外文名:Reduced Gigabit Media Independent Interface

- 特點:1000M網路接口,4線傳輸數據

簡介,通信原理,

簡介

同時兼容MII所規定的10/100 Mbps工作方式,支持傳輸速率:10M/100M/1000Mb/s ,其對應clk 信號分別為:2.5MHz/25MHz/125MHz。RGMII數據結構符合IEEE乙太網標準,接口定義見IEEE 802.3-2000。

採用RGMII的目的是降低電路成本,使實現這種接口的器件的引腳數從25個減少到14個。

通信原理

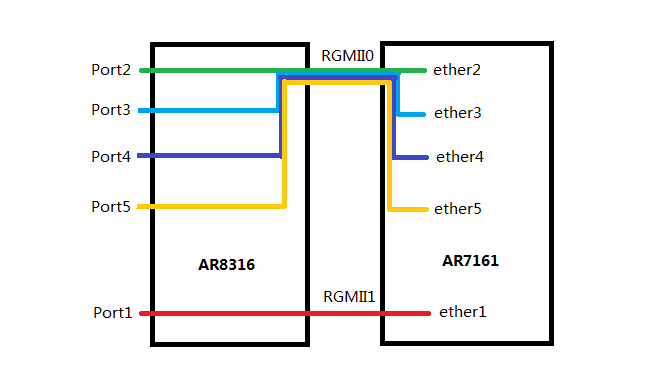

一般用於MAC和PHY之間的通信。

傳送器:

◎ GTX_CLK——吉比特TX..信號的時鐘信號(125MHz)

◎ TXD[3..0]——被傳送數據

◎ TX_CTL——傳送控制

註:在千兆速率下,向PHY提供GTX_CLK信號,TXD、TXEN、TXER信號與此時鐘信號同步。否則,在10/100M速率下,PHY提供 TXCLK時鐘信號,其它信號與此信號同步。其工作頻率為25MHz(100M網路)或2.5MHz(10M網路)。

接收器:

◎ RX_CLK——接收時鐘信號(從收到的數據中提取,因此與GTXCLK無關聯)

◎ RXD[3..0]——接收數據

◎ RX_CTL——接收控制

◎ COL——衝突檢測(僅用於半雙工狀態)

◎ CRS——載波監聽

管理配置(控制和狀態信息):

◎ MDC——配置接口時鐘

◎ MDIO——配置接口I/O

RGMII接口相對於GMII接口,在TXD和RXD上總共減少8根數據線。

RGMII is a reduced pin count interface that can simplify design by reducing the interface pin count from the 25pins used in the GMII interface to 12. It can lower system cost compared to existing GMII or TBI interfaces by reducing the number of layers required to route high density networking solutions. Using RGMII, fewer pins are required for the MAC/switch ASIC, which can reduce the MAC/switch cost by enabling smaller die sizes than would be possible with GMII or TBI. However, the RGMII specification calls for a timing delay on both the receive signal and the transmit signal for each port that must be implemented in a board level trace. These trace lengths are typically arranged in a spiral on the board that takes approximately one square inch of board space per trace. Broadcom offers an alternative timing solution that eliminates the need for the timing delay traces. Assuming a one-inch space requirement per trace for both transmit and receive signals on 48 ports, elimination of the timing delay traces can save 96 square inches of layout space.