PAE,英文名稱Physical Address Extension的縮寫,物理地址擴展。

PAE

實現

PAE,英文名稱Physical Address Extension的縮寫,物理地址擴展。

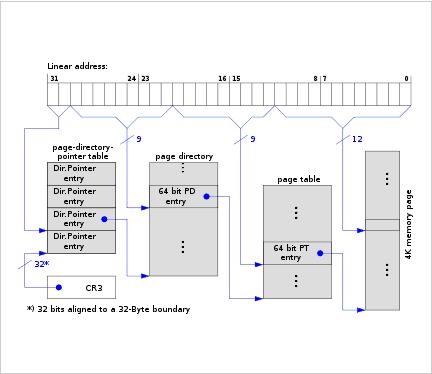

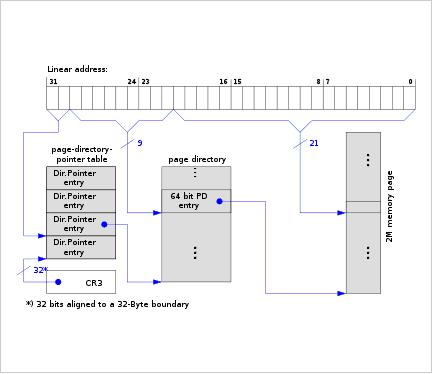

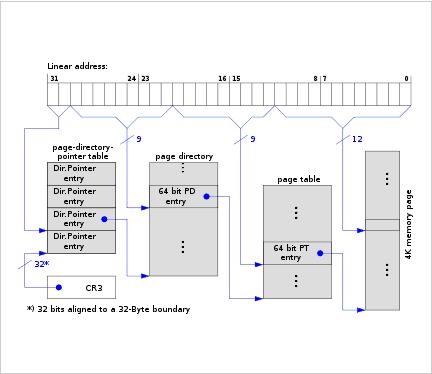

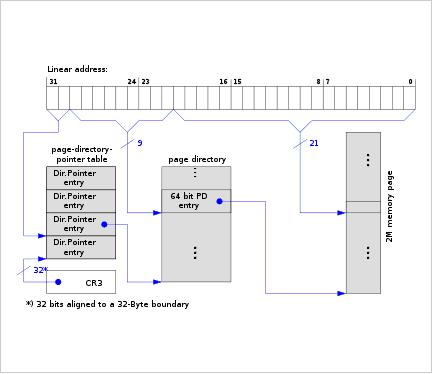

PAE,物理地址擴展,是基於x86 的伺服器的一種功能,它使運行 Windows Server 2003, Enterprise Edition 和 Windows Server 2003,Datacenter Edition 的計算機可以支持...

抗菌後效應(postantibiotic effect,PAE):抗菌藥物與細菌接觸一定時間後,藥物濃度逐漸下降,降到最小抑菌濃度(MIC)以下,或藥物全部排出以後,仍然對細菌的生長繁殖有...

“PAE王國”由CREATE BAI創立於20世紀。他在倫敦開了第一家店,推出了一系列標誌性產品,其中包括著名的包包,PAE從此享譽國際時裝界。隨著時間的流逝,這家著名的...

PAE,(Pout-Pin)/Pdc,為射頻輸出功率與耗散的直流功率之比。...... PAE,(Pout-Pin)/Pdc,為射頻輸出功率與耗散的直流功率之比。 PAE=(Pout-Pin)/Pdc 其中,Po...

PAE,英文名稱Physical Address Extension的縮寫,物理地址擴展。...... 網路訪問技術的核心部分是PAE(連線埠訪問實體)。在訪問控制流程中,連線埠訪問實體包含3部分:認證者-...

PAE即聚醯胺環氧氯丙烷樹脂,適用於製造各種具有濕強度的紙張,除用作濕強劑以外,還可用作乳液松香膠及強化松香膠的助留劑,中性施膠劑的增效劑,陽離子澱粉改性劑...

增稠劑PAE 外觀為白色乳液二pN值7。含固量(20±2)},乳液黏度(20℃)1000~3000mPa·s。主要成分是丙烯酸和甲基丙烯酸交聯共聚物的按鹽。適於用作棉、滌/棉混紡...

泰劇《我的女孩》由泰國Halo娛樂公司出品,由亞瑞克·阿莫蘇帕西瑞(Pae),艾絲特·蘇普莉拉(Esther)主演。該劇於2018年7月16日在泰國首播。...

概述PAE高階生物導能檢測儀是一種集數字腦電圖、地形圖、腦電監護三位於一體的多功能儀器。其數據準確、波幅穩定、波形無失真、無創無損、彌補影像學對臟器功能...

Ruen Pae Resort位於大城,是家2星級酒店。...... Ruen Pae Resort酒店還會提供一項住宿的免費政策:1名5歲以下的兒童在使用現有的床鋪時免費。...

win7 PAE模式是基於電腦x86 的伺服器的一種功能,它使運行 Windows Server 2003, Enterprise Edition 和 Windows Server 2003,Datacenter Edition 的計算機可以支持...

Paesch Jesus,阿魯巴籍足球運動員。...... Paesch Jesus .Euro Sport[引用日期2014-06-07] 詞條標籤: 人物 V百科往期回顧 詞條統計 瀏覽次數:次 編輯次數:1...

Jennifer Pae,演員,主要作品《蓋斯》。...... Jennifer Pae,演員,主要作品《蓋斯》。外文名 Jennifer Pae 職業 演員 電影作品上映時間 劇名 扮演角色 導演 主演 ...

Scott Paetty是一名演員,參與作品有《現場直播》、《真相至上》等。...... Scott Paetty是一名演員,參與作品有《現場直播》、《真相至上》等。外文名 Scott Paett...

Eric Paeper ..[引用日期2014-05-07] 詞條標籤: 娛樂人物 , 人物 V百科往期回顧 詞條統計 瀏覽次數:次 編輯次數:5次歷史版本 最近更新: 創建者:oohusn猜...

歌曲: Aalikadae Pali Palikadae Paembar詞條標籤: 娛樂 V百科往期回顧 詞條統計 瀏覽次數:次 編輯次數:2次歷史版本 最近更新: 創建者:楓島HO736...

抗生素的後效應(Postantibiotic Effect, PAE)是指細菌在接觸抗生素後雖然抗生素血清濃度降至最低抑菌濃度以下或已消失後,對微生物的抑制作用依然維持一段時間的效應。...

抗生素的抗菌後效應(Postantibiotic effect, PAE)是指細菌接觸抗生素一定時間,當藥物消除後,細菌生長受到持續抑制的效應。抗菌後效應已成為抗生素藥效學的一個重要指標...

濕強劑主要在造紙行業中套用。不同的紙種其用量大不相同,如(衛生紙、果袋紙、板紙、可濕水面紙等)。濕強劑現在主要是以PAE濕強劑為主。生產廠也是很多,大都...

Pae Old school 風格 澳大利亞 we hard dance MITT Old school 澳大利亞 we hard dance Brenton NR Old school 風格 澳大利亞 NR成員 JINJIN Old school 風格 德國...

亞瑞克·阿莫蘇帕西瑞(Pae),1984年9月2日出生在泰國,歌手、演員。他畢業於瑪希隆大學,後進入演藝界,出演過電影《鬼肢解》、《致命切割》中的男主角。...