基本介紹

- 中文名:Direct Digital Frequency Synthesis

- 外文名:直接數字式頻率合成器

- 簡稱:DDS

- 頻率解析度:0.001Hz

簡述,原理,

簡述

直接數字式頻率合成器(Direct Digital Frequency Synthesis簡稱DDS或DDFS)是近年來發展起來的一種新的頻率合成技術。它的主要優點是:相對頻寬很寬、頻率轉換時間極短(可小於20ns)、頻率解析度很高(典型值為0.001Hz)、全數位化結構便於集成、輸出相位連續、頻率、相位和幅度均可實現程控。因此,能夠與計算機緊密結合在一起,靈活地實現多種通信調製方式。

典型的DDS由相位累加器、ROM波形存儲表、D/A變換器和低通濾波器組成。相位累加器由N位加法器與N位累加暫存器級聯構成。ROM中存有一個周期的正弦或餘弦函式的幅度值。相位累加器在參考時鐘的作用下,將頻率控制數據fr進行線性相位累加,當相位累加器累積滿量時就會產生一次溢出,完成一個周期性的動作,這個周期就是DDS合成信號的一個頻率周期,累加器的溢出頻率就是DDS輸出的信號頻率。

基於DDS技術的調製器,一般還具有頻率暫存器、相位暫存器、調幅暫存器等單元。這些單元結合DDS中的基本單元可以非常方便地實現各種調製方式。

對於基帶信號,其頻寬一般較窄,因此在很多套用場合中都是根據Nyquist採樣定理,再結合工程實際,採用2.5~4倍的基帶信號最高頻率進行採樣,其採樣率記為。而作為載波的DDS輸出波形,其頻率相對較高,系統時鐘頻率更高。系統時鐘頻率即是載波的採樣率,因此,一般有。如果用基帶信號對載波進行正交調製,即是數位訊號的相乘,要求基帶和載波應具有相同的數據速率。所以,在進行正交調製之前必須對基帶數位訊號進行插值濾波,提高其數據速率。

提高基帶信號的數據速率有兩種途徑:一種是簡單的數據保持方法;另一種是嚴格的插值濾波法。

原理

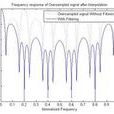

嚴格的插值濾波是先經過零值內插,然後再濾波得到。待插值序列記為,插值之後的序列記為,內插因子記為I,則有:設零值內插後得到序列為。經過低通濾波變成。及其頻譜示於圖2中。

其中;

可見和的頻譜是相同的,只不過是以為周期,而則是以為周期罷了。要想從得到,只需將通過以為通帶邊緣頻率的低通濾波器即可。該低通濾波器可用FIR線形相位濾波器實現。按照網路易位定理,可將FIR濾波器中的乘法運算移到低採樣率一側以減小計算工作量,得到其等效的高效結構,如圖3。

當插值比I較大時,直接把採樣率工作一次完成,從計算工作量和存儲量來說,都不如經過兩次或兩次以上轉換來得經濟。因為如果設計的是FIR最佳等波紋濾波器,則濾波器階數既受通帶和阻帶容限的影響,又受過度頻寬和採樣率的影響。過度頻寬過小,決定了濾波器的階數將很高,最終引起計算量很大。而單級實現遇到的正是過度頻寬過小的問題。如果採用多級實現,每一級的過度頻寬變大,濾波器階數減小,最終計算量反而比單級實現更小。

插值濾波器中經常用到一種稱為CIC的濾波器(Cascade Integrator-comb Filter 級聯梳狀濾波器)。CIC濾波器可以用來實現抽取器和內插器,它具有結構簡單、規整,需要的存儲量小的優點。由於它不需要乘法器,加之濾波器的所有係數均為1,而且利用積分環節減少了中間過程的存儲量,因此常常用在高速採樣(高速採樣使得乘法器個數太多)和插值比很大(插值比大使得FIR濾波器的階數過高,要存的係數太多)的場合。

CIC濾波器可以用DSP或現場可程式門陣列(FPGA)來實現。但是DSP實現高速插值濾波有困難,而FPGA具有設計簡單、技術成熟、設計周期短以及VHDL語言中濾波器參數N、M、R修改容易等優點。加之CIC濾波器具有不需要乘法器、暫存器個數要求較多的特點,正好符合FPGA的適用範圍。