基本介紹

- 中文名:Hi3512

- 生產公司:海思半導體

- 類型:通信媒體處理器

- 領域:通信媒體

- 支持協定:H.264和MJPEG等

處理器介紹,主要特點,套用領域,

處理器介紹

視頻處理單元能夠支持H.264 Main Profile、Baseline Profile、MJPEG、JPEG等多種協定的實時編解碼;支持H.264編解碼90fps@D1;支持高清1.3M Pixels@30fps,支持最大300萬象素的Jpeg抓拍。H264 Main Profile強大的編碼算法極大的提高了視頻質量,並且能夠靈活的提供場編碼或者幀編碼,為客戶支持不同的顯示終端提供了方便;視頻處理單元還支持雙碼流編碼,即MJPEG和H264可以同時編碼。圖形處理單元能夠提供De-interlace算法處理、靈活的運動檢測;支持視頻、圖形縮放;支持OSD。豐富的外圍接口方便滿足設備規格需求,有效降低整機BOM成本。

主要特點

CPU核心

ARM926EJ-S,16KB指令Cache和16KB數據Cache

內嵌2KB指令緊耦合存儲器

哈佛結構的32位RISC處理器

內置MMU,支持多種開放式作業系統

工作頻率可達到264MHz

視頻編解碼

H.264 Main [email protected]編解碼

H.264 Baseline [email protected]編解碼

MJPEG/JPEG Baseline編解碼

視頻處理性能

雙碼流編碼(H.264/MJPEG)

具備320fps@CIF編解碼能力

主子碼流編解碼90fps@D1

支持1.3M pixels@25fps~3M pixels@5fps

支持JPEG抓拍3M Pixels@5fps

CBR/VBR碼率控制,32kbit/s~20Mbit/s

圖形處理

De-interlace前處理

視頻、圖形縮放

4個區域的前處理OSD疊加

4層視頻後處理OSD硬體圖像疊加

對比度拉升、色彩增強

4個區域的視頻遮擋

宏塊級的SAD、MV信息輸出,支持靈活的運動偵測

空域、時域去噪

音頻編解碼

可以通過ARM核心實現多種音頻、語音編解碼功能

最多16路音頻實時編碼

支持雙向語音對講

安全引擎

硬體實現AES/DES/3DES多種加解密算法

數字水印技術

視頻接口

輸入:

− 2路BT.656/601 YCrCb 4:2:2,8bit,54MHz

− 1路SMPTE296M 720P高清接口,Y/C 4:2:2,16bit

− CCD和CMOS數字接口

輸出:

− 1路BT.656 YCrCb 4:2:2, 8 bits

音頻接口

2個I2S音頻接口

8/16/32位採樣位寬,採樣率可配置(4KHz~48KHz)

外圍接口

PCI接口

− 符合PCI V2.3通訊協定標準

− 兼容miniPCI

− 支持主從模式

3個UART接口、IR接口、I2C接口、SPI主從接口、GPIO接口

SDIO2.0接口

USB 1.1 Host接口、USB 2.0 OTG接口

1個MII接口,支持10/100 Mbit/s網路擴展

支持RTC,RTC可獨立供電

外部存儲器接口

DDR2 SDRAM接口

− 32/16 bit數據位寬

− 最大支持512MByte

NOR Flash接口

− 8 bit數據位寬

− 2個片選,每個片選最大支持32MByte

SDK

提供基於Linux SDK包

提供H.264的高性能PC解碼庫

晶片物理規格

功耗

− 600mW典型功耗

− 支持多級省電模式

工作電壓

− 核心電壓:1.2V

− IO電壓:3.3V,容限電壓為5V

− DDR2 DRAM接口電壓:1.8V

封裝

− 441 pin TFBGA封裝

− 0.8mm管腳間距,19mm×19mm

套用領域

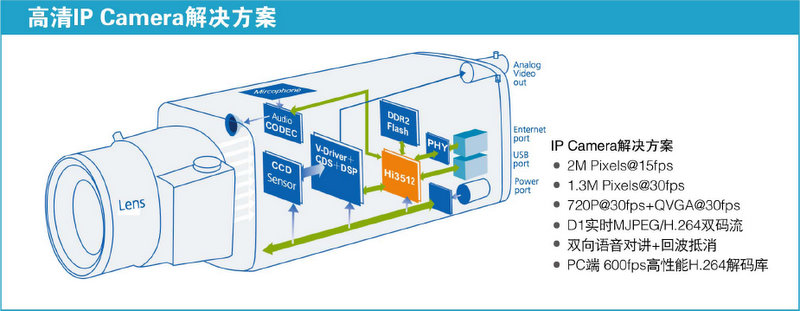

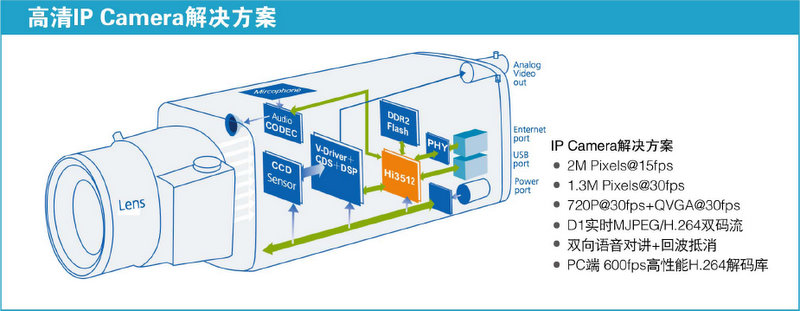

高清網路攝像機IPCamera Hi3512高清網路攝像機解決方案

Hi3512高清網路攝像機解決方案

Hi3512高清網路攝像機解決方案

Hi3512高清網路攝像機解決方案 網路視頻伺服器DVS(Digital video server)

硬碟錄像機DVR(Digital video recorder)