記憶體改進

邏輯Bank數量

DDR2 SDRAM中有4Bank和8Bank的設計,目的就是為了應對未來大容量晶片的需求。而DDR3很可能將從2Gb容量起步,因此起始的邏輯Bank就是8個,另外還為未來的16個邏輯Bank做好了準備。

封裝

封裝(Packages)DDR3由於新增了一些功能,所以在

引腳方面會有所增加,8bit晶片採用78球FBGA封裝,16bit晶片採用96球FBGA封裝,而DDR2則有60/68/84球FBGA封裝三種規格。並且DDR3必須是綠色封裝,不能含有任何有害物質。

突髮長度

突髮長度(BL,Burst Length)由於DDR3的預取為8bit,所以突發傳輸周期(BL,Burst Length)也固定為8,而對於DDR2和早期的DDR架構的系統,BL=4也是常用的,DDR3為此增加了一個4-bit Burst Chop(突發突變)模式,即由一個BL=4的讀取操作加上一個BL=4的寫入操作來合成一個BL=8的數據突發傳輸,屆時可通過A12

地址線來控制這一突發模式。而且需要指出的是,任何突發中斷操作都將在DDR3記憶體中予以禁止,且不予支持,取而代之的是更靈活的突發傳輸控制(如4bit順序突發)。

定址時序

定址時序(Timing)就像DDR2從DDR轉變而來後延遲周期數增加一樣,DDR3的CL周期也將比DDR2有所提高。DDR2的CL範圍一般在2至5之間,而DDR3則在5至11之間,且附加延遲(AL)的設計也有所變化。DDR2時AL的範圍是0至4,而DDR3時AL有三種選項,分別是0、CL-1和CL-2。另外,DDR3還新增加了一個時序參數——寫入延遲(CWD),這一參數將根據具體的

工作頻率而定。 從環保角度去看,降低功耗對業界是有著實實在在的貢獻的,全球的PC每年的耗電量相當驚人,即使是每台PC減低1W的幅度,其省電量都是非常可觀的。

降低功耗

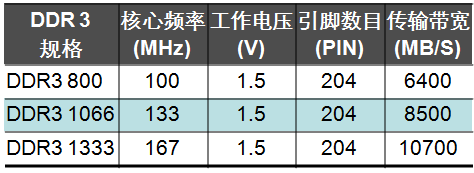

DDR3記憶體在達到高頻寬的同時,其功耗反而可以降低,其核心工作電壓從

DDR2的1.8V降至1.5V,相關數據預測DDR3將比現時DDR2節省30%的功耗,當然發熱量我們也不需要擔心。就頻寬和功耗之間作個平衡,對比現有的DDR2-800產品,DDR3-800、1066及1333的功耗比分別為0.72X、0.83X及0.95X,不但

記憶體頻寬大幅提升,功耗表現也比上代更好。

區別

規格

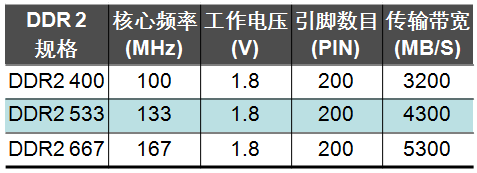

規格如右圖所示

新增功能

新增功能——重置(Reset)

重置是DDR3新增的一項重要功能,並為此專門準備了一個

引腳。DRAM業界已經很早以前就要求增這一功能,如今終於在DDR3身上實現。這一引腳將使DDR3的初始化處理變得簡單。當Reset命令有效時,DDR3記憶體將停止所有的操作,並切換至最少量活動的狀態,以節約電力。在Reset期間,DDR3記憶體將關閉內在的大部分功能,所以有數據接收與傳送器都將關閉。所有內部的程式裝置將復位,

DLL(延遲鎖相環路)與

時鐘電路將停止工作,而且不理睬

數據匯流排上的任何動靜。這樣一來,將使DDR3達到最節省電力的目的。

新增功能——ZQ校準

ZQ也是一個新增的腳,在這個引腳上接有一個240

歐姆的低公差參考電阻。這個引腳通過一個命令集,通過片上校準引擎(ODCE,On-Die Calibration Engine)來自動校驗

數據輸出驅動器導通電阻與ODT的終結電阻值。當系統發出這一指令之後,將用相應的

時鐘周期(在加電與初始化之後用512個時鐘周期,在退出自刷新操作後用256時鐘周期、在其他情況下用64個時鐘周期)對導通電阻和ODT電阻進行重新校準。

新增功能——CWD

作為寫入延遲之用

參考電壓分成兩個

對於記憶體系統工作非常重要的參考電壓信號VREF,在DDR3系統中將分為兩個信號。一個是為命令與地址信號服務的VREFCA,另一個是為

數據匯流排服務的VREFDQ,它將有效的提高系統數據匯流排的信噪等級。

SRT

根據溫度自動自刷新(SRT)為了保證所保存的數據不丟失,DRAM必須定時進行刷新,DDR3也不例外。不過,為了最大的節省電力,DDR3採用了一種新型的自動自刷新設計(ASR,Automatic Self-Refresh)。當開始ASR之後,將通過一個內置於DRAM晶片的溫度感測器來控制刷新的頻率,因為刷新頻率高的話,消電就大,溫度也隨之升高。而溫度感測器則在保證數據不丟失的情況下,儘量減少刷新頻率,降低工作溫度。不過DDR3的ASR是可選設計,並不見得市場上的DDR3記憶體都支持這一功能,因此還有一個附加的功能就是自刷新溫度範圍(SRT,Self-Refresh Temperature)。通過模式暫存器,可以選擇兩個溫度範圍,一個是普通的的溫度範圍(例如0℃至85℃),另一個是擴展溫度範圍,比如最高到95℃。對於DRAM內部設定的這兩種溫度範圍,DRAM將以恆定的頻率和電流進行刷新操作。

RASR

局部自刷新(RASR)這是DDR3的一個可選項,通過這一功能,DDR3

記憶體晶片可以只刷新部分邏輯Bank,而不是全部刷新,從而最大限度的減少因自刷新產生的電力消耗。這一點與移動型記憶體(Mobile DRAM)的設計很相似。

點對點連線

點對點連線(P2P,Point-to-Point)這是為了提高系統性能而進行了重要改動,也是與DDR2系統的一個關鍵區別。在DDR3系統中,一個

記憶體控制器將只與一個記憶體通道打交道,而且這個記憶體通道只能一個插槽。因此記憶體控制器與DDR3記憶體模組之間是點對點(P2P,Point-to-Point)的關係(單物理Bank的模組),或者是點對雙點(P22P,Point-to-two-Point)的關係(雙物理Bank的模組),從而大大減輕了地址/命令/控制與數據匯流排的負載。而在記憶體模組方面,與DDR2的類別相類似,也有標準DIMM(台式PC)、

SO-DIMM/Micro-DIMM(筆記本電腦)、

FB-DIMM2(伺服器)之分,其中第二代FB-DIMM將採用規格更高的AMB2(高級記憶體緩衝器)。不過有關DDR3記憶體模組的標準制定工作剛開始,引腳設計還沒有最終確定。