ACPI,即Advanced Configuration Power Interface.在G0工作狀態下,ACPI定義系統處理器的電源狀態,要么為活躍狀態(正在執行),要么為睡眠狀態(未執行)ACPI定義這樣的邏輯在每個CPU的偏置上,即OSPM通過轉換來切換不同的處理器電源狀態。

基本介紹

- 外文名:Advanced Configuration Power Interface

- 簡稱:C-state

- 含義:ACPI定義系統處理器的電源狀態

- 包括:不同的處理器電源狀態。

基本信息,基本簡介,

基本信息

ACPI Processor C-state

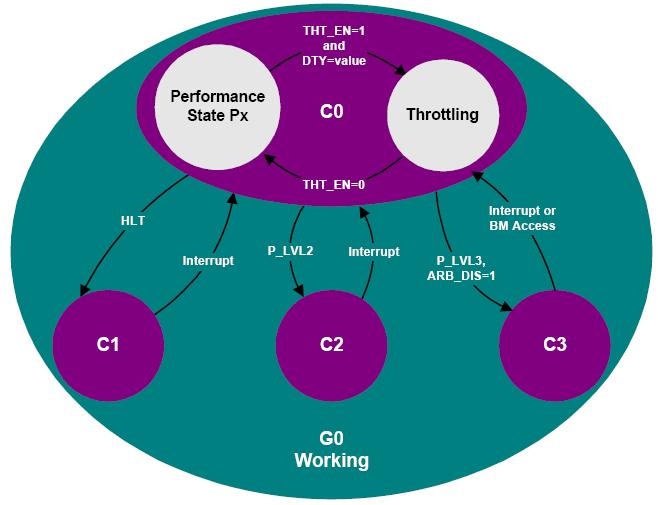

ACPI,即Advanced Configuration Power Interface.在G0工作狀態下,ACPI定義系統處理器的電源狀態,要么為活躍狀態(正在執行),要么為睡眠狀態(未執行)。處理器電源狀態被設計為C0,C1,C2,C3...Cn。C0電源狀態是活躍狀態,即CPU執行指令。C1到Cn都是處理器睡眠狀態,即和C0狀態相比,處理器處理器消耗更少的能源並且釋放更少的熱量。當進入睡眠狀態,處理器不執行任何指令。每個睡眠狀態都有一個和省電多少對應的延遲。一般來說,進入和退出的延遲越長,這個狀態越省電。為了保持能量,OSPM在空閒時將處理器置於其中一個支持的睡眠狀態中。在C0狀態下,ACPI允許處理器的性能通過一個定義的節制過程發生改變,通過改變進入多種性能狀態(P-states). 處理器的電源狀態.

ACPI定義這樣的邏輯在每個CPU的偏置上,即OSPM通過轉換來切換不同的處理器電源狀態。這個邏輯是可選的,在FADT表和處理器對象中有描述。FADT表中的這些欄位和標誌描述了硬體的對稱性,以及處理器對象對特別的CPU時鐘邏輯包含的位置(在P_BLK暫存器塊和_CST對象中有描述)。

P_LVL2和P_LVL3暫存器提供可選的支持,將系統處理器置於C2或者C3狀態。P_LVL2暫存器將排好序的處理器置於C2狀態,P_LVL3將排好序的處理器置於C3狀態。C3狀態的額外支持通過匯流排主狀態和仲裁禁止位被提供(PM1_STS暫存器中的BM_STS位和PM2_CNT暫存器中的ARB_DIS位)。系統軟體通過讀取P_LVL2或者P_LVL3暫存器數據來進入C2或者C3狀態。硬體必須精確的將處理器放在恰當的時鐘狀態,通過對相應的P_LVLx暫存器的讀操作。平台必須定義可選的接口來允許OSPM使用_CST對象進入C-state。

基本簡介

處理器的電源狀態支持是對稱的,通過FADT表和P_BLK接口;OSPM假設同一系統里的所有的處理器都在相同的電源狀態下。如果處理器有不對稱的電源狀態支持,BIOS將通過FADT表選擇和使用所有處理器最低的相同的電源狀態。例如,如果CPU0支持所有的電源狀態乃至C3,但是CPU1僅支持C1,那么OSPM將僅將空閒的處理器置於C1(CPU0將不會被置於C2和C3狀態)。注意C1必須被支持,C2和C3是可選的。

處理器電源狀態C1

所有的處理器必須支持這種狀態。這種狀態的支持是通過一個本地的處理器指令(HLT或者mwait),並且認為不需要晶片組的硬體支持。這種狀態的硬體延遲必須足夠的低,使得OSPM在決定是否使用該狀態時不需要考慮延遲方面的問題。除了將處理器置於一種電源狀態,這個狀態沒有其他的軟體可見的效果。在C1狀態下,處理器可以保持系統cache裡面的內容。

硬體可以以任何理由退出該狀態,但必須是在有中斷到達處理器的情況下。

處理器電源狀態C2

這種電源狀態不是必需的。如果存在,該狀態能夠更好的省電,它通過使用P_LVL2命令暫存器或者由_CST提供的另一種機制來使處理器進入該狀態。這個狀態的最壞情況下的硬體延遲在FADT的表裡面有聲明,OSPM可以根據這個信息來決定什麼時候C1狀態應該被C2狀態代替。除了將處理器置於一種電源狀態,該狀態沒有其他的軟體可見效果。OSPM假設C2比C1更省電,但是退出的延遲比C1要高。

C2電源狀態是一種可選的ACPI時鐘狀態,需要晶片組的硬體支持。時鐘邏輯由一個接口組成,可以用來被操縱使處理器精確的進入C2電源狀態。在C2電源狀態下,處理器被認為能夠保持其cache的一致性;例如,匯流排控制器和多處理器的活動可以發生而不破壞cache裡面的內容。

C2狀態將處理器置於一種低功耗的狀態,圍繞多處理器和匯流排控制器系統做最佳化。當存在匯流排控制器或者多處理器活動時(這一條件將阻止處理器進入C3狀態),OSPM將使一個空閒狀態下的處理器群體進入C2狀態。處理器簇能夠在C2狀態下監視匯流排控制器或者多核CPU訪問記憶體的行為。

硬體可以以任何理由退出該狀態,但必須是在有中斷到達處理器的情況下。

處理器電源狀態C3

系統對C3處理器電源狀態的支持也是可選的. 如果存在,這種狀態比C1和C2狀態更加節省功耗. 使用P_LVL3命令暫存器或者_CST機制可以進入C3狀態. 這種狀態的最壞的硬體延遲在FADT表中聲明了,OSPM可以通過這一信息來決定什麼時候需要進入C3狀態而不是C1或者C2狀態. 當在C3狀態中,處理器的cache保持著狀態但是處理器沒有窺視匯流排控制器,或者多核CPU進行訪存.

硬體可以以任何理由退出這種狀態,但必須是因為一個中斷投遞到了該處理器,或者當BM_RLD被設定時,一個匯流排控制器企圖訪存.

OSPM負責保證cache的一致性.在單處理器環境下,這可以通過使用PM2_CNT.ARB_DIS匯流排控制器仲裁暫存器來保證匯流排控制器的活動不會發生在C3狀態下. 在多處理器環境下,處理器的cache可以通過flush和invalidate來保持一致性.

有兩種機制支持C3電源狀態:

1. 在進入C3狀態之前,讓OSPM flush和invalidate cache

2. 提供一種硬體機制,阻止控制器寫記憶體(只支持UP)

在第一種情況下,OSPM將在進入C3之前flush系統的cache. 由於flush系統的cache通常有很大的延遲,OSPM只對多核平台的空閒處理器支持這種情況. flush cache通過ACPI定義的一種機制來完成.

單處理器平台提供一種硬體功能,OSPM將嘗試將平台置於一種模式,當處理器處於C3模式,這種模式組織系統匯流排控制器來寫記憶體。一旦匯流排控制器請求一個訪問,CPU將從C3中被喚醒,並且重新使能匯流排控制器訪問.

OSPM使用BM_STS位來決定要進入的電源狀態是C2還是C3. BM_STS是一個可選的bit位,表示匯流排控制器是活躍的. OSPM使用這一位來決定在C2和C3之間的策略. 頻繁的匯流排控制器活動將CPU的電源狀態降到C2,沒有匯流排控制器活動將CPU的電源狀態提升到C3. OSPM保持BM_STS的一個變化歷史來決定CPU電源狀態的策略.

用在C3里的最後一個硬體特性是BM_RLD位. 這一位決定匯流排控制器的訪問是否導致Cx電源狀態的退出. 如果這一位被設定,一旦有匯流排控制器訪問,Cx將退出. 如果該位被復位為零,匯流排控制器的訪問將不會導致電源狀態的退出. 在C3狀態中,匯流排控制器的申請需要CPU轉換回C0狀態,但是在C2狀態中,這樣的轉換將不

是必須的.在C3狀態下,OSPM可以設定這一位,在C1或C2狀態下,可以清除該位.