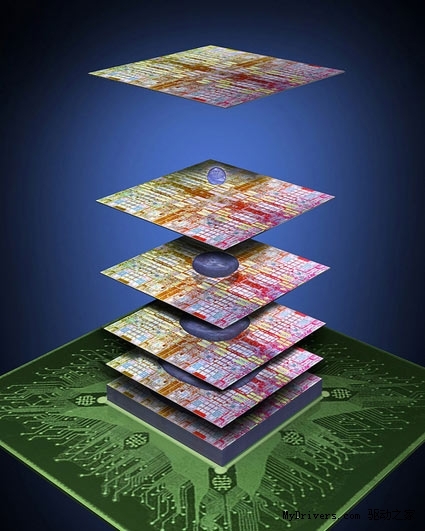

3D晶圓級封裝,英文簡稱(WLP),包括CIS發射器、MEMS封裝、標準器件封裝。

基本介紹

- 中文名:3D晶圓級封裝

- 外文名:WLP

3D晶圓級封裝,英文簡稱(WLP),包括CIS發射器、MEMS封裝、標準器件封裝。

3D晶圓級封裝,英文簡稱(WLP),包括CIS發射器、MEMS封裝、標準器件封裝。...... 3D封裝封裝特點 編輯 3D晶圓級封裝,英文簡稱(WLP),包括CIS發射器、MEMS封裝、標準器...

所謂“封裝技術”是一種將積體電路用絕緣的塑膠或陶瓷材料打包的技術。以CPU為例,實際看到的體積和外觀並不是真正的CPU核心的大小和面貌,而是CPU核心等元件經過封裝...

3D引擎是將現實中的物質抽象為多邊形或者各種曲線等表現形式,在計算機中進行相關計算並輸出最終圖像的算法實現的集合。 3D引擎就像是在計算機內建立一個“真實的世界...

3D記憶體晶片是通過3D封裝技術,將多層DRAM堆疊而成的新型記憶體。3D記憶體晶片能提供很高的記憶體容量和記憶體頻寬,其中混合記憶體立方體(Hybrid Memory Cube)和高頻寬記憶體(High ...

我們最常見的就是四種,幀連續、幀封裝、上下格式和左右格式。其中幀封裝,就是現在最流行的藍光3D。...

3DCG,全稱是3D computer graphics,意思是三維計算機圖形。...... 3DCG,全稱是3D computer graphics,意思是三維...心理射線渲染提供的一部分Softimage和Maya三維封裝...

3Dsuit是一套捕捉套裝,融合了導航系統和角定位系統,還配有Inertial Labs OSv3慣性感測器,可將動作數據傳輸至PC機。...

3D磁存儲器,即3D XPoint(發音three dee cross point),是一種由英特爾和美光科技於2015年7月宣布的非易失性記憶體(NVM)技術。英特爾為使用該技術的存儲設備冠名...

《電子封裝結構設計》是2017年西安電子科技大學出版社出版的一本圖書,作者是田文超、劉煥玲、張大興。...

SOP封裝的套用範圍很廣,而且以後逐漸派生出SOJ(J型引腳小外形封裝)、TSOP(薄小外形封裝)、VSOP(甚小外形封裝)、SSOP(縮小型SOP)、TSSOP(薄的縮小型SOP)及SOT(...

《高級電子封裝(原書第2版)》系統地介紹了電子封裝的相關知識,涵蓋了封裝材料與套用、原料分析技術、封裝製造技術、基片技術、電氣考慮因素、機械設計考慮因素、熱...

三維電子封裝的矽通孔技術 所屬類別 科技 >> 電工電子 >> 電子技術 作者:【美】John H Lau(劉漢誠)著 叢書名:電子封裝技術叢書 出版日期:2014年7月 書號:...

《手把手教你架構3D遊戲引擎》一書作者姜雪偉,電子工業出版社2016年11月出版...... 遊戲引擎架構、3D引擎底層封裝、3D引擎封裝、遊戲設計實現、地圖編輯器、3D可程式...

三星電子高端存儲晶片封裝測試項目生產線主要生產基於3D垂直快閃記憶體晶片的固態硬碟,該項目的竣工投產,使西安高新區的三星晶片工廠成為目前三星在海外投資的唯一一個集存儲...

Delta3D是一款由美國海軍研究學院(Naval Postgraduate School)開發的全功能遊戲與仿真引擎。...

《微電子封裝技術》是2011年中國科學技術大學出版社出版的圖書。本書比較全面、系統、深入地論述了在電晶體和積體電路(IC)發展的不同歷史時期出現的典型微電子封裝...

《電子製造與封裝》是2010年3月電子工業出版社出版的圖書,作者是杜中一。...... 5.5.2 三維(3D)封裝5.6 封裝材料5.6.1 封裝材料概述5.6.2 金屬封裝材料...

Java 3D是Java語言在三維圖形領域的擴展,是一組套用編程接口(API)。利用Java 3D提供的API,可以編寫出基於網頁的三維動畫、各種計算機輔助教學軟體和三維遊戲等等。...

CST Studio Suite 2008 包含最新SP5全模組完整版,3D電磁設計全系列軟體這是豪華套裝(完整版-全模組),包括了所有CST 2008開發產品!相對於2006B來說,2008性能得到了...

Java 3D是Java語言在三維圖形領域的擴展,是一組套用編程接口(API)。利用Java 3D提供的API,可以編寫出基於網頁的三維動畫、各種計算機輔助教學軟體和三維遊戲等等。...

3D遊戲引擎是包括3D圖形的各種算法整合起來,提供便捷的SDK接口以方便別人在這個基礎上開發遊戲的模組。3D遊戲引擎還包括聲音、圖形、物理、人工智慧等多種開發功能。....

POP即封裝體疊層技術,再集成為相同外形邏輯和存儲晶片封裝體,而疊層封裝能將具有相同外形的邏輯和存儲晶片的封裝體進行再集成,而不會產生在採用堆疊邏輯-記憶晶片...

VOLCANO是一款MMORPG(大型多人線上角色扮演)3D網路遊戲的開發引擎,用作支持用戶快速並簡單地開發具有真實遊戲環境和豐富遊戲玩點的遊戲,具有完全自主的智慧財產權,且未...

3D眼鏡接收頭是專用3D快門式眼鏡的一款紅外線產品,3D眼鏡接收頭是將光電二極體、發射管和信號調理IC集成到單片小尺寸封裝內,有助於降低3D眼鏡的重量,同時接收器的...