非對稱多核處理器用少量通用處理核心來處理需要較高軟體靈活性的功能

基本介紹

- 中文名:非對稱多核處理器

- 類型:計算機硬體

- 類別:處理器

- 特點:處理更多任務

概述,技術背景,非對稱多核處理器的優勢,智慧型分組引擎,流量管理器,線速安全協定處理器,支持高效 SoC 通訊,

概述

非對稱多核處理器用少量通用處理核心來處理需要較高軟體靈活性的功能,同時用大量的硬體加速器來處理儘可能多的任務。硬體任務調度軟體可管理核心與加速器之間的任務流。這種方法通常能將功耗減半並提升效率,因為所有必需的功能塊都包含在同一SoC 中。非對稱多核處理器可最大限度地提高核心與加速器的利用率,其優勢在於能將硬體加速器處理的所有任務都交由可程式加速器來處理,而僅將那些需要極高處理靈活性的複雜任務留給核心處理。相對於傳統多核SoC 而言,非對稱多核SoC 的設計工作更加複雜,不過一旦設計完成,非對稱多核SoC 就會給系統設計提供“量身打造的”方案,以將通用處理核心的要求減輕一半。

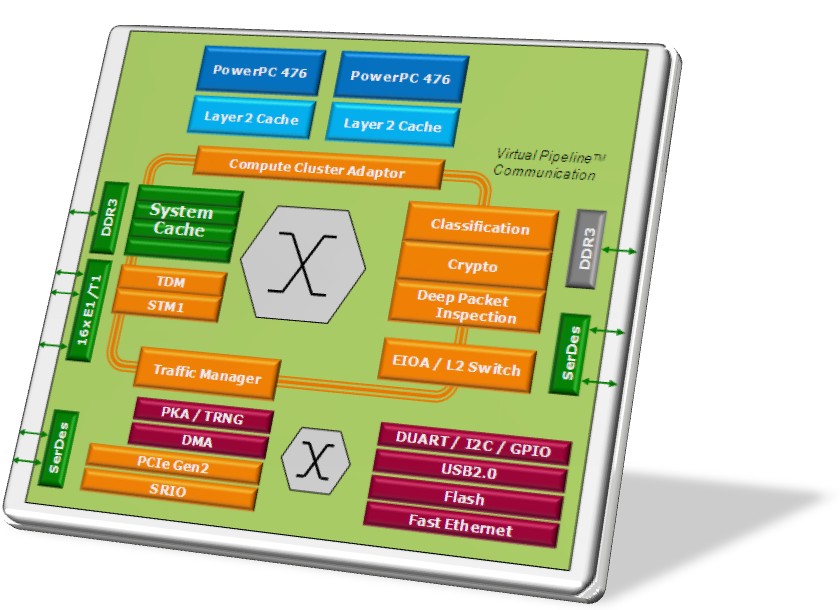

圖:LSI2012年3月新推出的Axxia 非對稱多核通信處理器AXM2500

技術背景

隨著演進分組系統(EVS)、SAE(系統架構演進)、LTE-Advanced 等各類部署的實施,在不久的將來將對無線網路提出新的要求,當前基礎設施的處理能力將實現多個數量級的提升,這就要求新型SoC 架構必須具備良好的擴展能力,以在控制成本的前提下滿足不斷上升的頻寬需求。

一些新技術如加強型智慧型路由/調度、通過IP包頭壓縮算法【網際網路協定報頭壓縮(IPHC)、穩健報頭壓縮(RoHC)】提升吞吐量,以及利用DPI對惡意流量嚴格過濾和控制技術等開始被廣泛套用,這些都是計算密集型的處理任務,對晶片處理能力提出了更高的要求。而可將靈活的處理器核心與一套硬體加速引擎完美相結合的非對稱多核SoC 非常適用於上述要求。

利用非對稱多核架構實現的高性能系統,能用少數強大的通用核心實現功耗最小化,提供確定性性能,並通過硬體加速引擎將CPU資源解放出來。LSI公司憑藉其在通信領域的領先技術,研發出Axxia 通信處理器等新一代非對稱架構,LSI公司的非對稱多核處理器具有靈活的片上路由技術,可實現硬體工作調度功能。非對稱多核通信處理器憑藉其獨特的優勢,能夠充分地滿足新一代通信基礎設施的要求。

對稱式多核處理器與非對稱多核處理器的對比

傳統(即對稱式)多核處理器與非對稱多核處理器都將通用多核處理器與硬體加速器結合在一起使用,其不同之處在於通用處理器和專用處理器所占的比例以及這些資源的使用方法。對稱多核處理器採用大量相同的通用處理器核心,其中任何處理器都能運行任何類型的執行緒,而少量專用硬體加速器引擎則在通用處理器控制之下運行。而在非對稱處理器中,通用處理器的數量相對較少,並與一系列專門運行計算強度較高、對時延敏感性強的特定任務的專用加速器引擎結合使用。此外,上述專用引擎還能夠在不占用通用處理器任何管理資源的情況下自動運行,執行包括安全加密、流量管理和DPI等在內的任務。這種方案不僅可大幅降低功耗,同時還能提高效率,因為所有必需的功能模組都能在同一SoC中獲得。非對稱處理器的優勢在於,它能將特定任務委託給負責特定功能的專用硬體加速器,同時能將通用核心解放出來用以處理更加複雜或非特定性的工作。

就非對稱多核處理器而言,可讓通用處理核心與一系列能承擔儘可能多任務的硬體加速器配合工作,這些任務包括加密、流量管理和深層數據包檢測等。通用處理器可提供高度的軟體靈活性,而硬體加速器則負責提供確定的性能。硬體任務調度程式能協助管理核心與加速器之間的任務流。這種方案不光可大幅降低功耗,同時還能提高效率,因為所有必需的功能模組都能在同一的SoC 中獲得。非對稱處理器的優勢在於,它能將特定任務委託給負責特定功能的專用硬體加速器,同時能將通用核心解放出來用以處理更加複雜或非特定性的工作。正是由於採用了這種方法,非對稱多核解決方案才能大幅降低對通用處理核心的需求。

側重於硬體加速器的設計方案所具備的其主要一大優勢在於,能夠在不同的流量情況下確保實現確定性的性能。基於純軟體的CPU 核心性能在不同的處理要求下大相逕庭。非對稱多核eNodeB 設計方案具有始終一致的吞吐量、通過硬體加速技術實現快速的回響時間、以及採用SoC 方案實現更低的BOM 成本,所有這些優勢使非對稱多核eNodeB 設計從眾多傳統設計方案中脫穎而出。我們可對硬體加速模組進行精確的量身定製,以執行一系列特定的任務,從而不必在多個任務之間平衡處理能力。

非對稱多核處理器的實現樣例

LSI的Axxia 通信處理器即為非對稱架構的一種卓越實現樣例,適用於具有更高性能和更低功耗要求的新一代移動與企業網路。Axxia 通信處理器由高性能多核PowerPC處理器聯合體和一組特定功能的硬體加速器(如智慧型分組包數據處理、流量管理、IPSec 處理和DPI等經過矽驗證的IP模組)組成,這些硬體加速器能夠在不對多核聯合體造成不必要負擔的情況下,將恰當的計算資源投入到恰當的數據包上,提供快速路徑處理能力。

非對稱多核處理器的優勢

我們將在以下部分以LSI Axxia 通訊處理器為例,介紹可從硬體加速獲益的4個不同領域。

智慧型分組引擎

無線套用領域的一個主要需求就是查找分組報頭並在執行所需的報頭修改後進行數據包路由。在非對稱多核SoC 中,硬體引擎無需CPU 干預就能滿足上述要求,從而將CPU 核心從龐大的計算負荷中解放出來。就LSI Axxia 通訊處理器而言,這些引擎支持樹形最長前綴分類、ACL(訪問控制列表),而且在完全由硬體管理表格添加/刪除/更新情況下能支持基於哈希的線速狀態協定學習。同時,可對校驗和進行檢查並對輸入流量進行CRC 檢驗的PIC(數據包完整性檢查),也可作為該模組的一部分在硬體中提供支持。此外,作為協定處理的一部分,統計數據收集、狀態管理、計時器維護和動態資源分配等也都由可同時支持數百萬個通訊流的硬體進行管理。

上述硬體引擎具有高度多執行緒化的特點,使用簡單的從運行到完成的編程模型,因此無論流量數據包是什麼模式,其都能確保確定的吞吐量性能,從而實現始終如一的吞吐能力。

流量管理器

線速安全協定處理器

與安全相關處理的處理需求非常多,會占用大量通用CPU 處理能力。廣義上說,我們也可將此視為IPSec 處理和深度數據包檢查(DPI) 要求。根據負載與獨立流量情況的不同,有關任務所需的工作周期數也會千差萬別,因此基於通用CPU 核心的解決方案會由於其吞吐能力的不穩定與不確定而無法勝任。

以下例子展現了基於硬體的安全處理功能:

不妨構想這樣一種典型的情況,使用基於哈希的訊息驗證代碼(HMAC) 需要為實現AES 加密與SHA 驗證處理256B 的數據包。運行頻率為1.33GHz 的8 核通用CPU 若發揮100% 的核心處理能力,可處理約5Gbps 的流量。LSI Axxia 通訊處理器中基於硬體的安全協定處理器可處理6Gbps 的流量,而SoC 上4 個通用CPU 核心的負載為零。

LSI Axxia 處理器在SoC 中包含兩個用於處理IPSec 與DPI 要求的獨立硬體加速器引擎,從而可將起相同作用的通用核心徹底解放出來。IPSec 引擎可支持全套協定處理(3GPP 訪問、IPSec、SRTP、SSL-TLS-DTLS等)、多種加密(DES & 3DES、AES-GCM/CCM/CM(SRTP)、ARC4-40、128、Kasumi f8、SNOW3G f8等)、驗證(MD-5、SHA-1、SHA-2、AES 版本、Kasumi f9、SNOW3G f9等)、第4 代PRNG以及TRNG 與PKA(公共密鑰加速器)等。DPI 硬體引擎也包含在LSI ACP中,支持可用於過濾包含病毒和垃圾郵件的惡意流量的正則表達式掃描,並能對用於掃描的規則集進行動態更新。

支持高效 SoC 通訊

就傳統多核處理器而言,傳入的流量始終由CPU 核心接收。上述核心將接收到的部分流量路由至加速器引擎進行處理,然後再將處理後的流量回收至核心,從而實現部分任務的核外處理。LSI Axxia 除了幾個硬體加速器模組之外還有4 個PowerPC 核心。為了能夠高效路由片上流量,Axxia 通信處理器採用能實現任意流量路由的LSI 虛擬管線技術。流量可從輸入連線埠直接路由至硬體加速引擎,再路由到下一個加速引擎,傳輸路徑完全取決於特定流量的處理需求,與是否使用CPU 核心無關。

舉例來說,可先將乙太網接口接收到的流量傳送至解密引擎以對加密的流量進行解密,再直接路由至內容檢查引擎對包含病毒/垃圾郵件或其他惡意內容的流量進行過濾。如果認為流量是安全的,則可直接將其傳送到背板連線埠,無需通過CPU 核心。此外,我們也可根據需要將流量從輸入連線埠或加速引擎路由至CPU 核心進行進一步處理。

根據對每個數據包制定的各種分類決策,每個數據包或通訊媒體流在離開ACP 之前都可經過引擎與CPU 核心的任意路由組合。這種靈活性非常強大與便捷,有利於設計流經器件的通訊流。