在雙重匯流排結構中,主MPU通過局部匯流排訪問局部M和局部I/O,這時的工作方式與單匯流排情況是一樣的。也經常作為主設備訪問全局M和全局I/O。當其他並列微處理器需要訪問全局M和全局I/O時,必須由匯流排控制邏輯部件統一安排才能進行,這時該微處理器就是系統的主控設備。

基本介紹

- 中文名:雙重匯流排

- 外文名:Dual bus

- 定 義:微處理器就是系統的主控設備

- 套用學科:計算機硬體術語

概念,雙重匯流排錯誤周期,

概念

當其他並列微處理器需要訪問全局M和全局I/O時,必須由匯流排控制邏輯部件統一安排才能進行,這時該微處理器就是系統的主控設備。

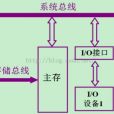

匯流排(Bus)是計算機各種功能部件之間傳送信息的公共通信幹線,它是由導線組成的傳輸線束, 按照計算機所傳輸的信息種類,計算機的匯流排可以劃分為數據匯流排、地址匯流排和控制匯流排,分別用來傳輸數據、數據地址和控制信號。匯流排是一種內部結構,它是cpu、記憶體、輸入、輸出設備傳遞信息的公用通道,主機的各個部件通過匯流排相連線,外部設備通過相應的接口電路再與匯流排相連線,從而形成了計算機硬體系統。在計算機系統中,各個部件之間傳送信息的公共通路叫匯流排,微型計算機是以匯流排結構來連線各個功能部件的。

雙重匯流排錯誤周期

當MCU正在進行錯誤異常處理或CPU正在執行RTI指令,從匯流排錯誤堆疊區取數據時,又發生了匯流排錯誤或地址錯誤,則MCU進入雙重匯流排錯誤周期。例如,MCU在處理匯流排錯誤時,需要將含有當成狀態的幾個字壓入堆疊,在壓入堆疊過程中,又出現了匯流排錯誤,則第二個匯流排錯誤就認為是一個雙重匯流排錯誤。在雙重匯流排錯誤周期期間,MCU驅動HALT信號為低,並處於暫停狀態,在這種情況下,只有復位才能使MCU重新開始工作。若前一匯流排錯誤異常處理已經完成,又出現了第二個匯流排錯誤,則不會引起雙重匯流排錯誤異常處理。

匯流排錯誤信號用於終止當前匯流排周期或終止指令的執行,從而進入匯流排錯誤異常控制周期。在匯流排錯誤異常處理過程中,BERR應保持有效,並一直保持到正常匯流排周期開始時為止。