基本介紹

數字積體電路是基於數字邏輯(布爾代數)設計和運行的,用於處理數位訊號的積體電路。根據積體電路的定義,也可以將數字積體電路定義為:將元器件和連線集成於同一半導體晶片上而製成的數字邏輯電路或系統。根據數字積體電路中包含的門電路或元、器件數量,可將數字積體電路分為小規模集成(SSI)電路、中規模集成MSI電路、大規模集成(LSI)電路、超大規模集成VLSI電路、特大規模集成(ULSI)電路和巨大規模積體電路(GSI,Giga Scale Integration)。

小規模積體電路包含的門電路在10個以內,或元器件數不超過10個;中規模積體電路包含的門電路在10~100個之間,或元器件數在100~1000個之間;大規模積體電路包含的門電路在100個以上,或元器件數在1,000~10, 000個之間;超大規模積體電路包含的門電路在1萬個以上,或元器件數在100,000~1,000,000之間;特大規模積體電路的門電路在10萬個以上,或元器件數在1,000,000~10,000,000之間。隨著微電子工藝的進步,積體電路的規模越來越大,簡單地以集成元件數目來劃分類型已經沒有多大的意義了,目前暫時以“巨大規模積體電路”來統稱集成規模超過1億個元器件的積體電路。

型號組成

數字積體電路的型號組成一般由前綴、編號、後綴三大部分組成,前綴代表製造廠商,編號包括產品系列號、器件系列號,後綴一般表示溫度等級、封裝形式等。如表0—1所示為TTL 74系列數字積體電路型號的組成及符號的意義。

邏輯功能

可將數字邏輯電路分成組合邏輯電路和時序邏輯電路兩大類。在組合邏輯電路中,任意時刻的輸出僅取決於當時的輸入,而與電路以前的工作狀態無關。最常用的組合邏輯電路有編碼器、解碼器、數據選擇器、多路分配器、數值比較器、全加器、奇偶校驗器等。在時序邏輯電路中,任意時刻的輸出不僅取決於該時刻的輸入,還與電路原來的狀態有關。因此,時序邏輯電路必須有記憶功能,必含有存儲單元電路。最常用的時序邏輯電路有暫存器、移位暫存器、計數器等。

具體的組合邏輯電路和時序邏輯電路不勝枚舉。由於它們的套用十分廣泛,所以都有標準化、系列化的積體電路產品,通常把這些產品叫做通用積體電路。與此相對應地把那些為專門用途而設計製作的積體電路叫做專用積體電路(ASIC)。

內部設計

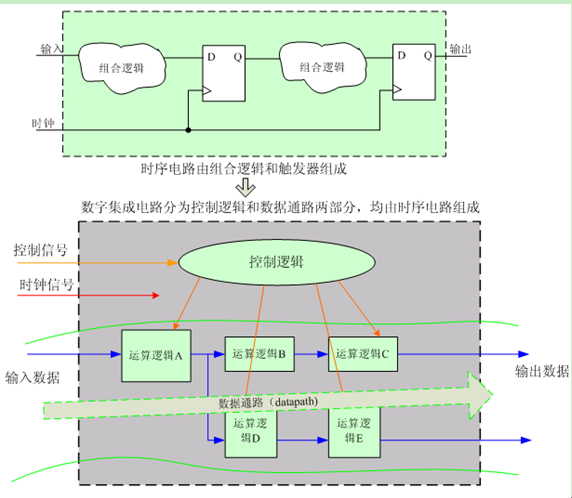

數字電路的組成:組合邏輯+暫存器(觸發器)。組合邏輯就是由基本門組成的函式,其輸出只會跟當前的輸入有關,在上面的例子中,第一個圖就是組合邏輯,只完成邏輯運算;而時序電路除了包含基本門之外,還包含存儲元件用例保存過去的信息,時序電路的穩態輸出不僅取決於當前的輸入,還與過去的輸入所形成狀態有關。第二個圖就是時序電路,在完成邏輯運算的同時,還可以把處理結果暫存起來,用以下一次的運算。

從功能上來看,數字積體電路內部可以分為數據通路(Data-path,也稱為數據路徑)和控制邏輯兩大部分。這兩大部分都是由大量的時序邏輯電路集成的,而且絕大部分都是同步的時序電路,因為時序電路被多個觸發器或暫存器分成若干節點,而這些觸發器在時鐘的控制下會按同樣的節拍來工作,可以簡化設計。在長期的設計過程中,已經積累了很多標準的通用單元,比如選擇器(也叫多路器,可以從多個輸入數據中選一個輸出)、比較器(用於比較兩個數的大小)、加法器、乘法器、移位暫存器等等,這些單元電路形狀規則,便於集成(這也是數字電路在積體電路中得到更好的發展的原因)。這些單元按設計要求連線在一起,形成數據通路,待處理的數據從輸入端經過這條通路到輸出端,便得到處理後的結果。同時,還需要由專門設計的控制邏輯,控制數據通路的各組成部件,按各自的功能要求和特定的時序關係和來配合工作。

類別說明

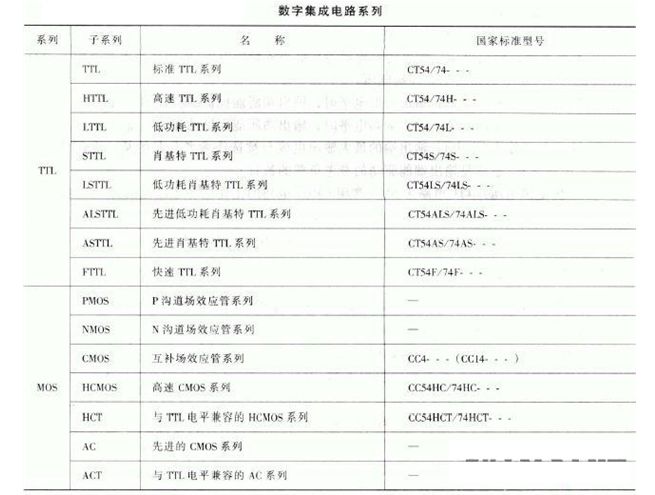

數字積體電路產品的種類很多,若按電路結構來分,可分成TTL和MOS 兩大系列。

TTL 數字積體電路是利用電子和空穴兩種載流子導電的,所以又叫做雙極性電路。MOS 數字積體電路是只用一種載流子導電的電路,其中用電子導電的稱為NMOS 電路;用空穴導電的稱為PMOS 電路:如果是用NMOS 及PMOS 複合起來組成的電路,則稱為CMOS 電路。

CMOS 數字積體電路與TTL 數字積體電路相比,有許多優點,如工作電源電壓範圍寬,靜態功耗低,抗干擾能力強,輸入阻抗高,成本低,等等。因而, CMOS 數字積體電路得到了廣泛的套用。

數字積體電路品種繁多,包括各種門電路、觸發器、計數器、編解碼器、存儲器等數百種器件。數字積體電路產品的系列見下表 。

國家標準型號的規定,是完全參照世界上通行的型號制定的。國家標準型號中的第一個字母"C" 代表中國;第二個字母"T" 代表TTL , "C" 代表CMOS。CT 就是中國的TTL數字積體電路, CC 就是中國的CMOS 數字積體電路。其後的部分與國際通用型號完全一致。

一般特性

TTL電路

(1)電源電壓範圍

TTL電路的工作電源電壓範圍很窄。S,LS,F系列為5V±5%;AS,ALS系列為5Y±10%。

(2)頻率特性

TTL電路的工作頻率比4000系列的高。標準TTL電路的工作頻率小於35MHz;LS系列TTL電路的工作頻率小 於40MHz;ALS系列電路的工作頻率小於70MHz;S系列電路的工作頻率小於125MHz;AS系列電路的工作頻率 小於200MHz.

(3)TTL電路的電壓輸出特性

當工作電壓為十5V時,輸出高電平大於2.4V,輸人高電平大於2.0V;輸出低電平小於0.4V,輸人低電平 小於0.8V。

(4)最小輸出驅動電流

標準TTL電路為16mA;LS-TTL電路為8mA;S-TTL電路為20mA;ALS-TfL 電路為8mA;AS-TTL電路為⒛ mA。大電流輸出的TTL電路:標準TTL電路為48mA;LS-TTL電路為24mA;S-TTL電路為64mA;ALS-TTL電 路為24/48mA;AS-TTL電路為48/64mA。

(5)扇出能力(以帶動LS-TTL負載的個數為例)

標準TTL電路為40;IS-TTL電路為20;S-TTL電路為50;ALS-TTL電路為 20;AS-TTL電路為50。大電流 輸出的TTL電路:標準TTL電路為120;LS-TTL電路為60;S-TTL電路為160;ALS-TTL電路為60/120;AS -TTL電路為120/160。

對於同一功能編號的各系列TTL積體電路,它們的引腳排列與邏輯功能完全相同。比如,7404,74LS04, 74A504,74F04,74ALS04等各積體電路的引腳圖與邏輯功能完全一致,但它們在電路的速度和功耗方面存 在著明顯的差別。

CM0S電路

(1)電源電壓範圍

積體電路的工作電源電壓範圍為3~18V,74HC系列為2~6V。

(2)功耗

當電源電壓VDD=5V時,CM0S電路的靜態功耗分別是:門電路類為2.5~5μW;緩衝器和觸發器類為5~20μW;中規模積體電路類為25~100μW,

(3)輸人阻抗

CM05電路的輸入阻抗只取決於輸人端保護二極體的漏電流,因此輸人阻抗極高,可達108~1011Ω以上。所以,CM0S電路幾乎不消耗驅動電路的功率。

(4)抗干擾能力

因為它們的電源電壓允許範圍大,因此它們輸出高低電平擺幅也大,抗干擾能力就強,其噪聲容限最大值為45%VDD保證值可達30%VDD,電源電壓越高,噪聲容限值越大。

(5)邏輯擺幅

CM0S電路輸出的邏輯高電平“1”非常接近電源電壓VDD邏輯低電平“0”接近電源Vss,空載時,輸出高電平VOH=VCC-0.05V,輸出低電平VOL=0.05V。因此,CM0S電路電源利用係數最高。

(6)扇出能力

在低頻工作時,一個輸出端可驅動50個以上CM0S器件。

(7)抗輻射能力

CMOS管是多數載流子受控導電器件,射線輻射對多數載流子濃度影響不大。因此,CM0S電路特別適用於航天、衛星和核試驗條件下工作的裝置。

CM0S積體電路功耗低,內部發熱量小,集成度可大大提高。又因為電路本身的互補對稱結構,當環境溫度變化時,其參數有互相補償作用,因而其溫度穩定性好。

(8)CM0S積體電路的製造工藝

CM0S積體電路的製造工藝比TTL積體電路的製造工藝簡單,而且占用矽片面積也小,特別適合於製造大規模和超大規模積體電路。

注意事項

①不允許在超過極限參數的條件下工作。電路在超過極限參數的條件下工 作,就可能工作不正常,且容 易引起損壞。TTL積體電路的電源電壓允許變化範圍比較窄,一般在4.5~5.5V之間,因此必須使用+5V穩 壓電源;CM0S積體電路的工作電源電壓範圍比較寬,有較大的選擇餘地。選擇電源電壓時,除首先考慮到 要避免超過極限電源電壓外,還要注意到,電源電壓的高低會影響電路的工作頻率等性能。電源電壓低, 電路工作頻率會下降或增加傳輸延遲時間。例如CM0S觸發器,當電源電壓由+15V下降到十3V時,其最高 工作頻率將從10MHz下降到幾十千赫。

②電源電壓的極性千萬不能接反,電源正負極顛倒、接錯,會因為過大電流而造成器件損壞。

③CM0S電路要求輸人信號的幅度不能超過VDD~VSS,即滿足VSS=V1=VDD。當 CM0S電路輸入端施加的電 壓過高(大於電源電壓)或過低(小於0V),或者電源電壓突然變化時,電路電流可能會迅速增大,燒壞器件,這種現象稱為可控矽效應。預防可控矽效應的措施 主要有:

·輸入端信號幅度不能大於VDD和小於0V;

·消除電源上的干擾;

·在條件允許的情況下,儘可能降低電源電壓,如果電路工作頻率比較低,用+5V電源供電最好;

·對使用的電源加限流措施,使電源電流被限制在30mA以內。

④對多餘輸人端的處理。對於CM0S電路,多餘的輸人端不能懸空,否則,靜電感應產生的高壓容易引起 器件損壞,這些多餘的輸人端應該接yDD或yss,或與其他正使用的輸人端並聯。這3種處置方法,應根據 實際情況而定。

對於TTL電路,對多餘的輸人端允許懸空,懸空時,該端的邏輯輸入狀態一般都作為“1”對待,雖然 懸 空相當於高電平,並不影響與門、與非門的邏輯關係,但懸空容易受干擾,有時會造成電路誤動作。因此 ,多餘輸人端要根據實際需要做適當處理。例如,與門、與非門的多餘輸人端可直接接到電源上;也可將 不同的輸人端公用一個電阻連線到電源上;或將多餘的輸人端並聯使用。對於或門、或非門的多餘輸人端 應直接接地。

⑤多餘的輸出端應該懸空處理,決不允許直接接到VDD或VSS,否則會產生過大的短路電流而使器件 損壞 。不同邏輯功能的CM0S電路的輸出端也不能直接連到一起,否則導通的P溝道MOS場效應管和導通的N溝道 MOS場效應管形成低阻通路,造成電源短路而引起器件損壞。除三態門、集電極開路門外,TTL積體電路的 輸出端不允許並聯使用。如果將幾個集電極開路門電路的輸出端並聯,實現“線與”功能時,應在輸出端 與電源之間接人上拉電阻。

⑥由於CM0S電路輸人阻抗高,容易受靜電感應發生擊穿,除電路內部設定保護電路外,在使用和存放時 應注意靜電禁止;焊接CM0S電路時,焊接工具應良好接地,焊接時間不宜過長,焊接溫度不要太高。更不 能在通電的情況下,拆卸,拔、插積體電路。

⑦多型號的數字電路之問可以直接互換使用,如國產的CC4000系列可與CD4000系列、MC14000系列直接互 換使用。但有些引腳功能、封裝形式相同的IC,電參數有一定差別,互換時應注意。

⑧注意設計工藝,增強抗干擾措施。在設計印製線路板時,應避免引線過長,以防止信號之間的竄擾和 對信號傳輸的延遲。此外要把電源線設計得寬一些,地線要進行大面積接地,這樣可減少接地噪聲干擾。 在CM0S邏輯系統設計中,應儘量減少電容負載。電容負載會降低CM0S積體電路的工作速度和增加功耗。