基本介紹

- 中文名:整合記憶體控制器

- 外文名:integrated memory controller

- 縮寫:IMC

- 研究公司:英特爾

產生背景

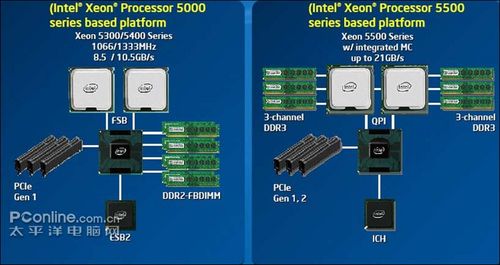

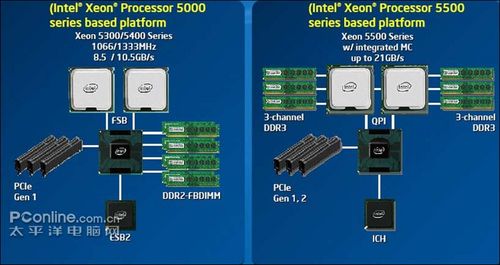

Xeon 5000與Xeon 5500區別圖示

Xeon 5000與Xeon 5500區別圖示

Xeon 5000與Xeon 5500區別圖示

Xeon 5000與Xeon 5500區別圖示整合記憶體控制器(integrated memory controller,IMC)是英特爾在其最新的Nehalem架構處理器中新加入的一種快速通道互聯技術,這也是Nehalem架構處理器全新採用的直連架構後...

記憶體控制器是計算機系統內部控制記憶體並且通過記憶體控制器使記憶體與CPU之間交換數據的重要組成部分。記憶體控制器決定了計算機系統所能使用的最大記憶體容量、記憶體BANK數、記憶體...

PCI記憶體控制器加速系統,降低功耗.筆記本電腦將會支持一項名為FRMT的技術(曾經代號Robson),中文名稱為英特爾迅盤。...

CPU內部整合記憶體控制器的最大缺點,就是對記憶體的適應性比較差,靈活性比較差,只能使用特定類型的記憶體,而且對記憶體的容量和速度也有限制,要支持新類型的記憶體就必須更新...

雙通道記憶體技術其實是一種記憶體控制和管理技術,它依賴於記憶體控制器發生作用,在理論上能夠使兩條同等規格記憶體所提供的頻寬增長一倍。它最早被套用於伺服器和工作站...

PCI-E控制器,即PCI-EXPRESS LANES控制器,可以支持顯示卡。在Lynnfield酷睿i7/酷睿i5處理器內部,除了像i7那樣整合了以往北橋的主要模組——記憶體控制器外,Intel連PCI...

MCP晶片不但提供了一般南橋晶片左右具有的控制PCI匯流排、IDE設備、USB接口,而且整合了目前功能最強大的音頻單元和網路晶片。在支持的記憶體規則方面,nForce 620-D可支持...

記憶體鏡像就像硬碟存儲的RAID 1。一旦其中一個頻道的記憶體發生故障,記憶體控制器就會...記憶體的增加促使整合水平的提高,記憶體的可靠性也影響該伺服器上所有虛擬機(VM)的...

Rambus的時鐘可以高達400MHz,而且僅使用了30條銅線連線記憶體控制器和RIMM(Rambus In-line MemoryModules,Rambus內嵌式記憶體模組),減少銅線的長度和數量就可以降低數據...

計算機中所有程式的運行都是在記憶體中進行的,因此記憶體的性能對計算機的影響非常大。記憶體(Memory)也被稱為記憶體儲器,其作用是用於暫時存放CPU中的運算數據,以及與硬碟...

如果大家對電腦的記憶體與硬碟有個清晰的概念的話就知道了,記憶體是我們不可存放檔案的,只有在運行程式時用上,是個臨時存儲器;而C糟為我們可用的存儲空間,就相當於是...

是一家由計算機存儲行業15年以上資深人士共同發起成立的高科技企業, 於2010年開始規劃“無間道”品牌的一系列記憶體模組產品.優道成立伊始,不斷整合產業的上下遊資源,...

l 基於全新的四核心MAC Pro工作站,(標配:兩顆 INTEL XEON 2.4G四核心4處理器,每個 Intel Xeon” 處理器均配有一個整合記憶體控制器,直接將記憶體與處理器連線,3GB...

因為一般的記憶體主要是採用傳統的64位並行設計,即北橋晶片的記憶體控制器與記憶體模組...一般來說,使用伺服器能夠支持的最大的DIMM。這通常可以為系統潛在整合(或故障...

減少記憶體整體讀寫的次數,另外還針對繪圖需要而增加了繪圖控制器,並提供區塊搬移...DDRII 是DDR原有的SLDRAM聯盟於1999年解散後將既有的研發成果與DDR整合之後的未來...