概念 低功率電路被認為是一種耗能較低的積體電路。當

積體電路 正變得越來越複雜時,為了適應這一變化,在進行積體電路設計時就不得不考慮

功耗 的要求,低功率系統越來越受到重視。

低功率電路的確定 研究背景 隨著科學技術的發展,電器產品功能不斷增強,越來越多的電器產品中使用電子控制電路。JFKLMNEI < IOOP《家用和類似用途電器的安全第一部分:通用要求》中規定:如果電器產品的

電子線路 是低功率電路,並且在器具的其它部份中,對電擊、火災危險、機械危險或危險的功能失常的保護不依賴於此電子線路的正常工作,則該電子線路不進行非正常試驗,否則,需進行電子線路的非正常試驗。非正常試驗是檢驗電器產品在發生故障、不正常工作的情況下是否安全的一個非常重要的檢驗項目,如不合格,則產品將被判安全不合格,禁止進出口和安裝使用。由此可以看出低功率電路的確定在進行電子線路非正常工作時,具有重要意義。

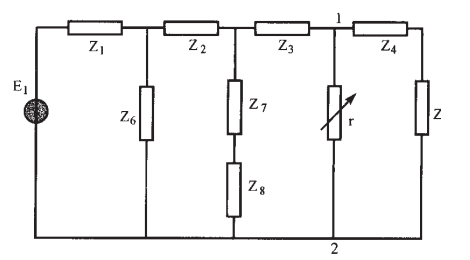

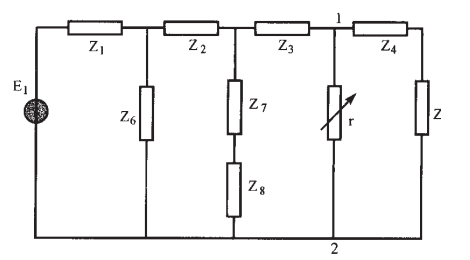

圖1 含線性元件的集中參數電路 低功率電路的確定方法 (1)可變電阻器法

根據低功率電路的定義,我們可以用一個可變電阻器來進行測量。優點是操作比較簡單。缺點是由於電阻的選擇或操作不當,可能找不到低功率點,實際操作中,經常發生電路故障。

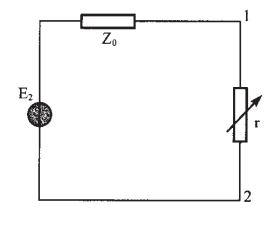

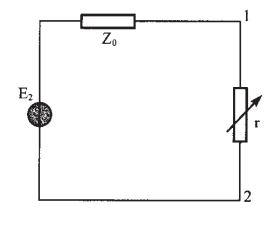

圖2 戴維南等效電路 (2)計算法

根據分析、計算電路的特性來確定低功率電路。對於含線性元件的集中參數電路(如圖1), 為確定某一被調查點(例如節點1)是否為低功率點,我們在節點1與節點2之間串聯一

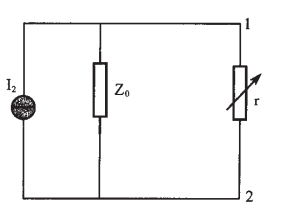

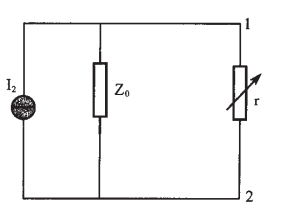

可變電阻 r,根據戴維南定理,任何線性有源二端網路對外的等效電路可用一電壓源與內部等效阻抗相串聯之電路表示(如圖2);或根據諾頓定理,任何線性有源二端網路對外的等效電路可用一電流源與內部等效阻抗相併聯之電路表示(如圖3)。

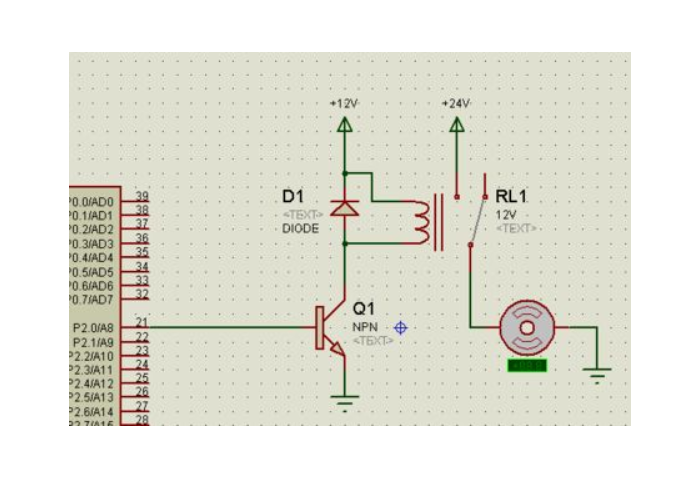

圖3 諾頓等效電路 (3)EDA(Electronic Design Automation)方法

EDA電子設計自動化技術在電子設計和製造領域飛速地發展。其中ProtelInternational公司的Protel軟體可以實現電子產品從電學概念設計到生成物理生產數據的全過程,以及這中間的所有分析、仿真和驗證。Protel提供了高級數模器件混合仿真功能,其仿真引擎使用的是伯克利分校的SPICE3f5/Xspice,它可精確地仿真各種器件構成的電路。

研究結論 低功率電路的確定還有其他方法,研究暫列舉了三種方法,從上面的分析可以看出,每種方法都有其優缺點,只有對各種方法靈活運用,並不斷總結電路的規律,才能準確、快速地找出低功率點和低功率電路。

低功率電路的套用及其實現方案 低功率套用 在電池供電模式下,一些攜帶型電腦工作時間可達6個小時以上。由於受攜帶型電腦的實際尺寸和重量限制,不允許加風扇或其它

冷卻器 。也限制了電池的大小和重量,因此增加電池尺寸延長電池工作時間的做法是不可行的。

低功率系統的另一個例子是蜂窩電話。它們能將用於系統控制的

微處理器 、

模擬電路 、數字電路和RF電路一起集成到很小的封裝中,電池在充電一次後,能在“接收、待機”模式下工作一整天,並可以有一小時的通話時間。

一般來說,低功率系統必須面對與低功耗有關的額外性能限制,而系統設計都將功耗作為其中的一項重要性能指標。半導體工藝和電路結構的發展為元器件性能帶來巨大進步,同時也帶來功耗問題。許多情況下要平衡性能與功耗的關係非常困難,但利用適當的功率控制方法或創新性設計可以獲得多種解決方案。

降低供電電壓會產生兩種副作用。首先,電路工作電壓越低,則速度越慢。如果其它因素都保持不變的話,會減小電容充放電的電流或負載驅動電流。其次,較低的電壓將導致較低的輸出功率或較低的信號幅度,這會產生噪聲和信號衰減問題。

產生功耗的原因 整體的功耗取決於諸多因素,如基底技術、封裝密度、外部環境、產品性能和供電電壓。在實際套用中,往往速度越高功耗越大。電阻上消耗的功率表示為12R,它通常由負載器件和寄生元件產生。不管採用何種技術都會或多或少地存在這方面的功耗,在電阻性負載電路如模擬電路中更是如此。當採用深亞微米技術時,電路中的導線(金屬導線)和層間寄生電阻會產生靜態阻抗功耗,在動態功耗中也要消耗一定的

電流 。

有源器件 的正常工作模式可用一條轉移曲線和某些I—V特性來描述,工作點電壓與電流的乘積是功率的函式,適用於全部有源器件。該乘積是一個靜態值,對無源和有源器件來說,它包含了漏電流和偏置電流。

在CMOS電路中。理想情況下,I—V轉移曲線是一個瞬態函式。當I—V轉移曲線跨越門限時,從一個狀態轉移到另一個狀態不消耗功率。但在實際套用中。轉移曲線並不是理想的方形。因此每次狀態轉移時都會有大的(潛在性)開關電流。理論上看,在狀態轉移過程最壞情況下,具有零內阻的開關器件會在電源與地之間形成直接短路的現象。

在CMOS電路中,最大的功耗來自於內部和外部電容的充放電,通常用W/Hz來表示每個門電路的功耗。據此,就可以計算後級的門或輸出負載(包括電路封裝和PCB導線)的電容充放電所需的功率。峰值電流I=C(V/T),V約等於CMOS電路的電源電壓,T是上升或下降沿時間,C是後級負載電容,因此峰值電流通常都比較大。平均開關功率P=C(V)2F,此時C是指輸出端的

負載電容 ,V是

供電電壓 ,F則是開關頻率。

功耗的系統成本 系統功率越大,所需要的電源電壓也越高,成本也就更昂貴,由此產生的影響涉及到電源匯流排、板上旁路電容、母板布線、電源線濾波器甚至電源電纜和熔絲等。另外,較大的供電電源需要更多的空間,因此可能會影響到系統的總體封裝。

電池尺寸、重量和成本取決於系統對整體功率的要求以及每次充電所要求的工作時間。一般情況下,電池越大成本越高。備份電池和充電器在尺寸與重量方面可能與原設備相當,因此會嚴重影響設備的便攜性。因此,系統整體功率要求得越低,在

電源 方面開銷就越少。同時小型電源產品占用空間小。自身功率消耗得也較少,因此會對系統整體功耗有益。

其它問題包括風扇與另外一些散熱元件的成本,當需要加速空氣流通時成本也會相應增加;散熱器與排熱管有助於熱源熱量的散發,但仍需將熱量從系統中排除出去。低成本的塑膠封裝不能適應高集成度IC的高功率特性要求。這迫使其採用具有熱量管理功能的昂貴封裝或其它更複雜的冷卻系統。

低功率電路的實現方案 IC 工業正尋求多種途徑來滿足低功率系統要求,其中一個途徑是將數字器件的

工作電壓 從5V變為3.3V,將模擬器件的電源電壓從+15V變為5V單電源。這些改變歸功於先進的矽片技術與電路結構。未來數字晶片工作電壓的發展趨勢將是2.5V、1.8V甚至更低的電壓,它們均是0.9V(電池電壓的最低極限)的倍數。器件的複雜度、更高的工作頻率和器件物理性質將共同促進這一發展趨勢。屆時亞微米幾何尺寸的更小型器件所具有的較薄

氧化層 將難以承受更高的電源電壓。

為滿足低功率系統要求,有些廠商還會採取在產品中增加 3V核心單元和宏的方法。這些產品經過最佳化能同時工作在3V或5V電源下,並具有相同的性能指標,利用特殊的接口單元,它們仍保留有5V電源接口。而影響供電電壓快速更新換代的最大障礙在於,現有的大量系統都採用5V電源,這些系統要求產品保留與其它5V(TIL)接口的後向兼容性。

圖1 含線性元件的集中參數電路

圖1 含線性元件的集中參數電路 圖2 戴維南等效電路

圖2 戴維南等效電路 圖3 諾頓等效電路

圖3 諾頓等效電路

圖1 含線性元件的集中參數電路

圖1 含線性元件的集中參數電路 圖2 戴維南等效電路

圖2 戴維南等效電路 圖3 諾頓等效電路

圖3 諾頓等效電路