工藝要素,(1)晶圓尺寸,(2)蝕刻尺寸,(3)金屬互連層,生產流程,(1) 矽提純,(2)切割晶圓,(3)影印(Photolithography),(4)蝕刻(Etching),(5)重複、分層,(6)封裝,(7)多次測試,工藝方向,兩種泄漏電流,1 SOI技術,2 Low K互連層技術,3應變矽技術,

工藝要素

隨著生產工藝的進步,CPU應該是越做越小?可為什麼現在CPU好像尺寸並沒有減少多少,那么是什麼原因呢?實際上CPU廠商很希望把CPU的集成度進一步提高,同樣也需要把CPU做得更小,但是因為現在的生產工藝還達不到這個要求。

生產工藝這4個字到底包含些什麼內容呢,這其中有多少高精尖技術的匯聚,CPU生產廠商是如何應對的呢?下文將根據上面CPU製造的7個步驟展開敘述,讓我們一起了解當今不斷進步的CPU生產工藝。

(1)晶圓尺寸

矽晶圓尺寸是在半導體生產過程中矽晶圓使用的直徑值。矽晶圓尺寸越大越好,因為這樣每塊晶圓能生產更多的晶片。比如,同樣使用0.13微米的製程在200mm的晶圓上可以生產大約179個

處理器核心,而使用300mm的晶圓可以製造大約427個處理器核心,300mm直徑的晶圓的面積是200mm直徑晶圓的2.25倍,出產的處理器個數卻是後者的2.385倍,並且300mm晶圓實際的成本並不會比200mm晶圓來得高多少,因此這種成倍的生產率提高顯然是所有晶片生產商所喜歡的。

然而,矽晶圓具有的一個特性卻限制了生產商隨意增加矽晶圓的尺寸,那就是在晶圓生產過程中,離晶圓中心越遠就越容易出現壞點。因此從矽晶圓中心向外擴展,壞點數呈上升趨勢,這樣我們就無法隨心所欲地增大晶圓尺寸。

總的來說,一套特定的矽晶圓生產設備所能生產的矽晶圓尺寸是固定的,如果對原設備進行改造來生產新尺寸的矽晶圓的話,花費的資金是相當驚人的,這些費用幾乎可以建造一個新的生產工廠。不過半導體生產商們也總是盡最大努力控制晶圓上壞點的數量,生產更大尺寸的晶圓,比如8086 CPU製造時最初所使用的晶圓尺寸是50mm,生產Pentium 4時使用200mm的矽晶圓,而Intel新一代Pentium 4 Prescott則使用300mm尺寸矽晶圓生產。300mm晶圓被主要使用在90納米以及65納米的晶片製造上。

(2)蝕刻尺寸

蝕刻尺寸是製造設備在一個矽晶圓上所能蝕刻的一個最小尺寸,是CPU核心製造的關鍵技術參數。在製造工藝相同時,電晶體越多處理器核心尺寸就越大,一塊矽晶圓所能生產的晶片的數量就越少,每顆CPU的成本就要隨之提高。反之,如果更先進的製造工藝,意味著所能蝕刻的尺寸越小,一塊晶圓所能生產的晶片就越多,成本也就隨之降低。比如8086的蝕刻尺寸為3μm,Pentium的蝕刻尺寸是0.90μm,而Pentium 4的蝕刻尺寸當前是0.09μm(90納米)。2006年初intel酷睿發布,採用65nm蝕刻尺寸,到2008年酷睿2已經發展到45nm蝕刻尺寸,2010年1月英特爾發布第一代Core i系列處理器採用32nm的蝕刻尺寸,2012年4月,英特爾發布第三代Core i系列處理器採用22nm蝕刻尺寸,2015年初第五代Core i系列處理器採用14nm蝕刻尺寸,直到2016年第七代Core i系列KabyLake架構的處理器還在延續使用14nm蝕刻尺寸。

此外,每一款CPU在研發完畢時其核心架構就已經固定了,後期並不能對核心邏輯再作過大的修改。因此,隨著頻率的提升,它所產生的熱量也隨之提高,而更先進的蝕刻技術另一個重要優點就是可以減小電晶體間電阻,讓CPU所需的電壓降低,從而使驅動它們所需要的功率也大幅度減小。所以我們看到每一款新CPU核心,其電壓較前一代產品都有相應降低,又由於很多因素的抵消,這種下降趨勢並不明顯。

我們前面提到了蝕刻這個過程是由光完成的,所以用於蝕刻的光的波長就是該技術提升的關鍵。目前在CPU製造中主要是採用2489埃和1930埃(1埃=0.1納米)波長的氪/氟紫外線,1930埃的波長用在晶片的關鍵點上,主要套用於0.18微米和0.13微米製程中,而目前Intel是最新的90納米製程則採用了波長更短的1930埃的氬/氟紫外線。

以上兩點就是CPU製造工藝中的兩個因素決定,也是基礎的生產工藝。這裡有些問題要說明一下。Intel是全球製造技術最先進且擁有工廠最多的公司(Intel有10家以上的工廠做CPU),它掌握的技術也相當多,後面有詳細敘述。AMD和Intel相比則是一家小公司,加上新工廠Fab36,它有3家左右的CPU製造工廠。同時AMD沒有能力自己研發很多新技術,它主要是通過

戰略合作關係獲取技術。

在0.25微米製程上,AMD和Intel在技術上處於同一水平,不過在向0.18微米轉移時落在了後面。在感覺無法獨自趕上Intel之後,AMD和摩托羅拉建立了

戰略合作夥伴關係。摩托羅拉擁有很多先進的電子製造技術,用於Apple電腦PowerPC的晶片HiPerMOS7(HiP7)就是他們完成的;AMD在獲得授權後一下子就擁有了很多新技術,其中部分技術甚至比Intel的0.13微米技術還要好。現在AMD選擇了IBM來共同開發65納米和45納米製造技術。它選擇的這些都是相當有前景的合作夥伴,特別是IBM,一直作為業界的技術領袖,它是第一個使用銅互連、第一個使用低K值介電物質、第一個使用SOI等技術的公司。AMD獲得的大多數技術很先進,而且對生產設備的要求不高,生產成本控制的很低,這也是AMD的優勢。

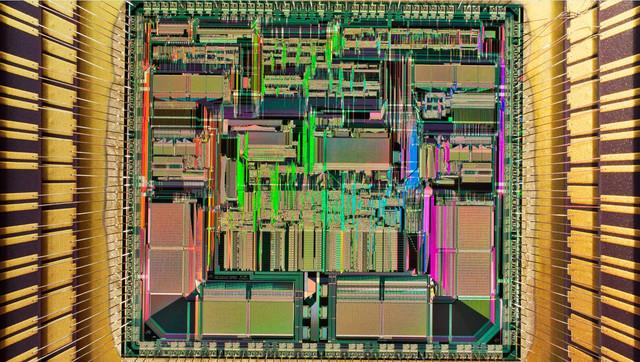

圖為AMD的新工廠Fab36中採用的APM 3.0 (Automated Precision Manufacturing)技術,可進一步實現製造的自動化,效率化。同時AMD還建造了自己的無塵實驗室。

(3)金屬互連層

在前面的第5節“重複、分層”中,我們知道了不同CPU的內部互連層數是不同的。這和廠商的設計是有關的,但它也可以間接說明CPU製造工藝的水平。這種設計沒有什麼好說的了,Intel在這方面已經落後了,當他們在0.13微米製程上使用6層技術時,其他廠商已經使用7層技術了;而當Intel準備好使用7層時,IBM已經開始了8層技術;當Intel在Prescott中引人7層帶有Low k絕緣層的銅連線時,AMD已經用上9層技術了。更多的互連層可以在生產上億個電晶體的CPU(比如Prescott)時提供更高的靈活性。

我們知道當電晶體的尺寸不斷減小而處理器上集成的電晶體又越來越多的時候,連線這些電晶體的金屬線路就更加重要了。特別是金屬線路的容量直接影響信息傳送的速度。在90納米製程上,Intel推出了新的絕緣含碳的二氧化矽來取代氟化

矽酸鹽玻璃,並同時表示這可以增加18%的內部互連效率。

生產流程

要了解

CPU的生產工藝,我們需要先知道CPU是怎么被製造出來的。

(1) 矽提純

生產CPU等晶片的材料是半導體,現階段主要的材料是

矽Si,這是一種非金屬元素,從化學的角度來看,由於它處於元素周期表中金屬元素區與非金屬元素區的交界處,所以具有半導體的性質,適合於製造各種微小的電晶體,是目前最適宜於製造現代

大規模積體電路的材料之一。

在

矽提純的過程中,原材料矽將被熔化,並放進一個巨大的石英熔爐。這時向熔爐里放入一顆晶種,以便矽晶體圍著這顆晶種生長,直到形成一個幾近完美的單晶矽。以往的矽錠的直徑大都是200毫米,而CPU廠商正在增加300毫米晶圓的生產。

(2)切割晶圓

矽錠造出來了,並被整型成一個完美的圓柱體,接下來將被切割成片狀,稱為

晶圓。晶圓才被真正用於CPU的製造。所謂的“切割晶圓”也就是用機器從單晶矽棒上切割下一片事先確定規格的矽晶片,並將其劃分成多個細小的區域,每個區域都將成為一個CPU的

核心(Die)。一般來說,

晶圓切得越薄,相同量的矽材料能夠製造的CPU成品就越多。

(3)影印(Photolithography)

在經過熱處理得到的矽氧化物層上面塗敷一種光阻(Photoresist)物質,紫外線通過印製著CPU複雜電路結構圖樣的模板照射矽基片,被紫外線照射的地方光阻物質溶解。而為了避免讓不需要被曝光的區域也受到光的干擾,必須製作遮罩來遮蔽這些區域。這是個相當複雜的過程,每一個遮罩的複雜程度得用10GB數據來描述。

(4)蝕刻(Etching)

這是CPU生產過程中重要操作,也是CPU工業中的重頭技術。蝕刻技術把對光的套用推向了極限。蝕刻使用的是波長很短的紫外光並配合很大的鏡頭。短波長的光將透過這些石英遮罩的孔照在光敏抗蝕膜上,使之曝光。接下來停止光照並移除遮罩,使用特定的化學溶液清洗掉被曝光的光敏抗蝕膜,以及在下面緊貼著抗蝕膜的一層矽。

然後,曝光的矽將被原子轟擊,使得暴露的矽基片局部摻雜,從而改變這些區域的導電狀態,以製造出N井或P井,結合上面製造的基片,CPU的門電路就完成了。

(5)重複、分層

為加工新的一層電路,再次生長矽

氧化物,然後沉積一層多晶矽,塗敷光阻物質,重複影印、蝕刻過程,得到含多晶矽和矽氧化物的溝槽結構。重複多遍,形成一個3D的結構,這才是最終的CPU的核心。每幾層中間都要填上金屬作為導體。Intel的Pentium 4處理器有7層,而AMD的Athlon 64則達到了9層。層數決定於設計時CPU的布局,以及通過的電流大小。

(6)封裝

這時的CPU是一塊塊晶圓,它還不能直接被用戶使用,必須將它封入一個陶瓷的或塑膠的封殼中,這樣它就可以很容易地裝在一塊電路板上了。封裝結構各有不同,但越高級的

CPU封裝也越複雜,新的封裝往往能帶來晶片電氣性能和穩定性的提升,並能間接地為主頻的提升提供堅實可靠的基礎。

(7)多次測試

測試是一個CPU製造的重要環節,也是一塊CPU出廠前必要的考驗。這一步將測試晶圓的電氣性能,以檢查是否出了什麼差錯,以及這些差錯出現在哪個步驟(如果可能的話)。接下來,晶圓上的每個CPU核心都將被分開測試。

由於SRAM(

靜態隨機存儲器,CPU中

快取的基本組成)結構複雜、密度高,所以快取是CPU中容易出問題的部分,對快取的測試也是CPU測試中的重要部分。

每塊CPU將被進行完全測試,以檢驗其全部功能。某些CPU能夠在較高的頻率下運行,所以被標上了較高的頻率;而有些CPU因為種種原因運行頻率較低,所以被標上了較低的頻率。最後,個別CPU可能存在某些功能上的缺陷,如果問題出在快取上,製造商仍然可以禁止掉它的部分快取,這意味著這塊CPU依然能夠出售,只是它可能是Celeron等低端產品。

當CPU被放進包裝盒之前,一般還要進行最後一次測試,以確保之前的工作準確無誤。根據前面確定的最高運行頻率和快取的不同,它們被放進不同的包裝,銷往世界各地。

工藝方向

在現有常規工藝的支撐下,CPU很難再向前發展,並且遇到越來越多的障礙,接下來討論CPU的繼續發展方向。

兩種泄漏電流

首先是門泄漏,這是電子的一種自發運動,由負極的矽底板通過管道流向正極的門;其次是通過電晶體通道的矽底板進行的電子自發從負極流向正極的運動。這個被稱作亞閾泄漏或是關狀態泄漏(也就是說當電晶體處於“關”的狀態下,也會進行一些工作)。這兩者都需要提高門電壓以及驅動電流來進行補償。這種情況自然的能量消耗以及發熱量都有負面的影響。

現在讓我們回顧一下

場效應電晶體中的一個部分——在門和通道之間的絕緣二氧化矽(silicon dioxide)薄層。這個薄層的作用就相當於一個電子屏障,用途也就是防止門泄漏。很顯然,這個層越是厚,其阻止泄漏的效果就越好。不過還要考慮它在通道中的影響,如果我們想要縮短通道(也就是減小電晶體體積),就必須減少這個層。在過去的10年中,這個薄層的厚度已經逐漸達到整個通道長度的1/45。目前,處理器廠商們正在做的是使這個層越來越薄,而不顧隨之增加的門泄漏。不過這個方式也有它的限度,Intel的技術員說這個薄層的最小厚度是2.3納米,如果低於這個厚度,門泄漏將急劇增大。這也是

摩爾本人提到的“漏電率快速上升”而制約

摩爾定律繼續前進。

到目前為止,處理器廠商還沒有對亞閾泄漏做什麼工作,不過這一情況很快就要改變了。操作電流和門操作時間是標誌電晶體性能的兩個主要參數,而亞閾泄漏對兩者有不小的影響。為了保證電晶體的性能,廠商們不得不提高驅動電流來得到想要的結果。這點在主機板的

供電系統和電源規範中有明顯體現,我們也可以理解為什麼越來越多的供電和散熱規範是Intel等CPU廠商提出的。

1 SOI技術

在所有的解決方案中,SOI(Silicon on Insulator,絕緣層上覆矽)看上去最有前景。關鍵很其實現很簡單:電晶體通過一個更厚的絕緣層從矽晶元中分離出來。

這樣做具有很多優點:首先,這樣在電晶體通道中就不會再有不受控制的電子運動,也就不會對電晶體電子特性有什麼影響;其次,在將閾值電壓載入到門電路上後,驅動電流出現前通道電離的時間間隔也減小了,也就是說,電晶體“開”和“關”狀態的切換性能提高了,這可是電晶體性能的第二大關鍵性能參數;同時在速度不變的情況下,我們可以也可以降低閾值電壓,或是同時提高性能和降低電壓。

舉個例子來說,如果閾值電壓保持不變,性能可以提高30%,那么如果我們將頻率保持不變而將注意力集中在節能性上,那么我們也可以節省大約50%的能耗。此外,在電晶體本身可以處理各種錯誤時(比如空間例子進入通道進行電離),通道的特性也變得容易預計了。而SOI不足在於必須減小電晶體漏極/源區域的深度,而這將導致電晶體阻抗的升高。同時,SOI技術也意味著電晶體的成本提高了10%。

2 Low K互連層技術

關於功耗和漏電問題,還有一個大家耳熟能詳的技術就是Low K互連層。

在

積體電路工藝中,有著極好熱穩定性、抗濕性的二氧化矽一直是金屬互聯線路間使用的主要絕緣材料。隨著互聯中導線的電阻(R)和電容(C)所產生的寄生效應越來越明顯,

低介電常數材料替代傳統絕緣材料二氧化矽也就成為積體電路工藝發展的又一必然選擇。

這裡的“K”就是介電常數,Low K就是低介電常數材料。Low K技術最初由IBM開發,當時的產業大背景是——隨著電路板蝕刻精度越來越高,晶片上集成的電路越來越多,信號干擾也就越來越強,所以IBM致力於開發、發展一種新的多晶矽材料。IBM聲稱,Low K材料幫助解決了晶片中的信號干擾問題。而Intel的目的是使用低介電常數的材料來製作處理器導線間的絕緣體。這種Low K材料可以很好地降低線路間的串擾,從而降低處理器的功耗,提高處理器的高頻穩定性。

在技術套用中,Low K材料最先出現在ATi的9600XT中。CPU方面,Prescott是Intel第一款使用7層帶有Low K絕緣層的CPU,同時使用了Carbon-Doped Oxide(CDO)(最新的低介電常數CDO絕緣體)絕緣體材料,減少了線到線之間的電容,允許提高晶片中的信號速度和減少功耗。

Low K目前最大缺點是實際套用效果不明顯,需要新的材料的介入,比如從有機材料領域尋求發展。Low K材料的開發速度可以說是空前迅猛的,前景光明,不過還是需要注意一些老問題,比如工藝不成熟、銅互連技術缺陷還有良品率問題等。此外目前的Low K材料可靠性還不高,不很耐高溫並且比較脆弱,nVidia就已經指出Low K材料的易碎性。

3應變矽技術

電晶體的結構也將有所改變。不過不是在數量上,通道的長度將從60nm下降到50nm,而其他東西則保持不變。實際上其他的東西都是由通道長度決定的,不論是電晶體的速度還是大小。為了保證有利因素髮揮同時減小負面因素,Intel會在應變矽(Strained silicon)以及新型的銅和含碳二氧化矽互連的低溫介電體上使用開始使用90納米技術。這個氧化物薄層非常的薄,僅有1.2納米厚,完全符合上面提到的厚度為通道長度的1/45,卻超過了Intel自己宣稱的2.3納米的極限值。

應變矽的使用目的和二氧化矽層相反,它是作為電子的禁止出現的,在其下的通道則是電子由發射端到接受端的路徑,電流越高,電子運動就越容易,速度也越快。通道一般是用矽製成的,不過在使用應變矽之後,就需要將原子拉長,那么電子在通過稀疏的原子格時遇到的阻抗就大大下降。Intel宣稱只需將矽原子拉長1%,就可以提高10-20%的電流速度,而成本只增加了2%。