地址匯流排 (Address Bus;又稱:位址匯流排) 屬於一種電腦匯流排 (一部份),是由CPU 或有DMA 能力的單元,用來溝通這些單元想要存取(讀取/寫入)電腦記憶體元件/地方的實體位址。

基本介紹

- 中文名:地址匯流排

- 外文名:Address Bus

- 所屬學科:計算機科學與技術

基本信息

技術指標

操作過程

第一代32位處理器

第一代32位處理器技術規範

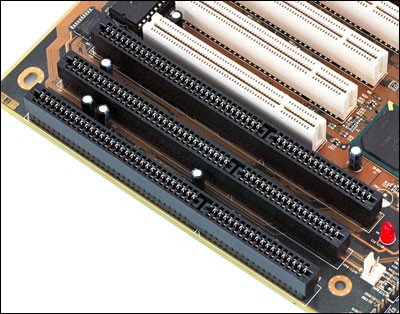

地址匯流排(圖2)

地址匯流排(圖2)標準分類

ISA技術

ISA技術

地址匯流排 (Address Bus;又稱:位址匯流排) 屬於一種電腦匯流排 (一部份),是由CPU 或有DMA 能力的單元,用來溝通這些單元想要存取(讀取/寫入)電腦記憶體元件/地方的實體位址。

第一代32位處理器

第一代32位處理器 地址匯流排(圖2)

地址匯流排(圖2) ISA技術

ISA技術地址匯流排 (Address Bus;又稱:位址匯流排) 屬於一種電腦匯流排 (一部份),是由CPU 或有DMA 能力的單元,用來溝通這些單元想要存取(讀取/寫入)電腦記憶體元件/地方的實體...

匯流排(Bus)是計算機各種功能部件之間傳送信息的公共通信幹線,它是由導線組成的傳輸線束, 按照計算機所傳輸的信息種類,計算機的匯流排可以劃分為數據匯流排、地址匯流排和控制...

地址匯流排(AddressBus;又稱:位址匯流排)屬於一種電腦匯流排(一部份),是由CPU或有DMA能力的單元,用來溝通這些單元想要存取(讀取/寫入)電腦記憶體元件/地方的實體位址。...

地址匯流排寬度 地址匯流排寬度決定了CPU可以訪問的物理地址空間,簡單地說就是CPU到底能夠使用多大容量的記憶體。16位的微機我們就不用說了,但是對於386以上的微機系統,...

地址線是用來傳輸地址信息用的。舉個簡單的例子:cpu在記憶體或硬碟裡面尋找一個數據時,先通過地址線找到地址,然後再通過數據線將數據取出來。 如果有32根.就可以...

控制匯流排(ControlBus)簡稱CB。控制匯流排主要用來傳送控制信號和時序信號。控制信號中,有的是微處理器送往存儲器和輸入輸出設備接口電路的,比如:讀/寫信號、片選信號...

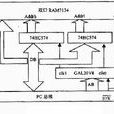

即存儲器的地址引腳數。 例如:現用2K*8位的靜態RAM晶片構成8K*8位存儲器,若CPU輸出的地址信號為20位。 片內地址匯流排就是11位(2Kb=211b )。 ...

系統匯流排(英語:System Bus)是一個單獨的計算機匯流排,是連線計算機系統的主要組件。這個技術的開發是用來降低成本和促進模組化。系統匯流排結合數據匯流排的功能來搭載信息,...

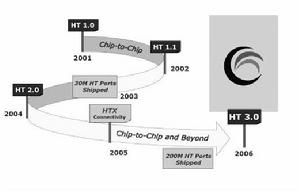

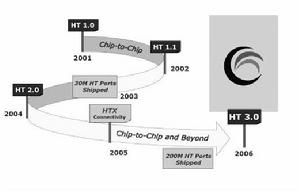

CPU匯流排,是PC系統中最快的匯流排,也是晶片組與主機板的核心。這條匯流排主要由CPU使用,用來與高速快取、主存和北橋(或MCH)之間傳送信息。...

地址匯流排(Address Bus)是一種計算機匯流排,是CPU或有DMA能力的單元,用來溝通這些單元想要訪問(讀取/寫入)計算機記憶體組件/地方的物理地址。數據匯流排的寬度,隨可定址的...

指令匯流排即用於傳送計算機指令信息,一般只從記憶體讀取指令信息到指令暫存器,屬於單向匯流排。現有馮.諾依曼架構中,指令匯流排和數據共享一條匯流排,在哈佛架構中,指令匯流排和...

匯流排技術就是將各部件連線到計算機處理器的一個元件。要連線的部件包括硬碟、記憶體、音響系統和視頻系統等。例如,要查看計算機在做什麼,一般是使用陰極射線管(CRT)...

地址空間(address space)表示任何一個計算機實體所占用的記憶體大小。比如外設、檔案、伺服器或者一個網路計算機。地址空間包括物理空間以及虛擬空間。...

匯流排系統是指微型計算機各部件之間傳送信息的通道。...... 插卡插入擴展槽後,地址信號經插卡上不同類型的擴展匯流排提供的地址匯流排寬數據的傳輸是匯流排最重要的使命。所...

存儲匯流排是指中央處理器CPU通過存儲匯流排和主存儲器和高速顯示卡傳輸數據。...... (用於傳遞數據);地址匯流排(用於傳遞主存儲器的地址);控制匯流排(用於各種內部控制指令的...

匯流排(Bus)是計算機各種功能部件之間傳送信息的公共通信幹線,它是由導線組成的傳輸線束, 按照計算機所傳輸的信息種類,計算機的匯流排可以劃分為數據匯流排、地址匯流排和控制...

用來保存當前CPU所訪問的記憶體單元的地址。由於在記憶體和CPU之間存在著操作速度上的差別,所以必須使用地址暫存器來保持地址信息,直到記憶體的讀/寫操作完成為止 。 ...

AB 即Address Bus;又稱:位址匯流排, 屬於一種電腦匯流排 (一部份),是由 CPU 或有 DMA 能力的單元,用來溝通這些單元想要存取(讀取/寫入)電腦記憶體元件/地方的實體...

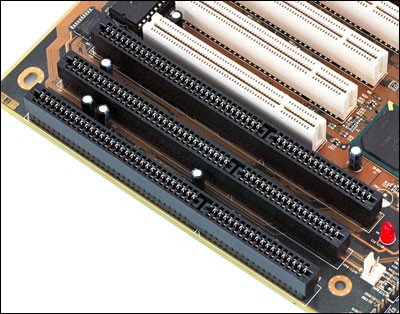

匯流排標準是系統與各模組、模組與模組之間的一個互連的標準界面。...... 2、常用工業標準匯流排a、PC匯流排--標準的匯流排IBMPC/-XT 20位地址線,8位數據線; IBMPC-A...