基本介紹

簡介

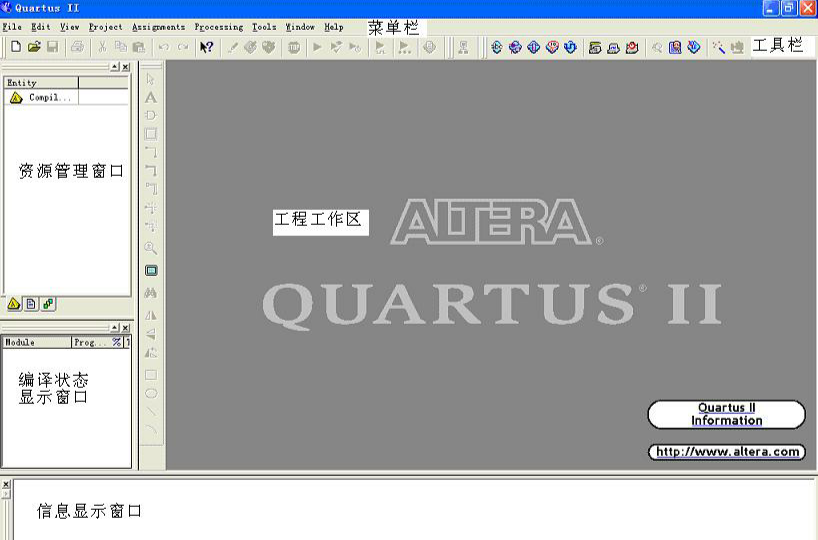

QuartusII圖示

QuartusII圖示

QuartusII圖示

QuartusII圖示Quartus II design 是最高級和複雜的,用於system-on-a-programmable-chip (SOPC)的設計環境。 Quartus II design 提供完善的 timing closure 和 LogicLock™ ...

Quartus II 是Altera公司的綜合性CPLD/FPGA開發軟體,原理圖、VHDL、VerilogHDL以及AHDL(Altera Hardware 支持Description Language)等多種設計輸入形式,內嵌自有的綜合器...

《基於Quartus II的計算機核心設計》是2007年清華大學出版社出版的圖書,作者是姜詠江。本書是介紹用QuartusⅡ6.0進行計算機設計的教材,書中以最新的手法設計了一種抗...

《基於QuartusII的FPGA/CPLD設計》是2006年電子工業出版社出版的圖書,作者是李洪偉。...

《基於QuartusII計算機核心設計》是2007年11月12號清華大學出版社出版的圖書,作者是姜詠江。...

《基於QuartusII的數字系統VerilogHDL設計實例詳解》是2010年電子工業出版社出版的圖書,作者是周潤景。...

《基於Quartus II的FPGA/CPLD設計與套用》是2009年電子工業出版社出版的一本圖書。...... 《基於Quartus II的FPGA/CPLD設計與套用》是2009年電子工業出版社出版的一...

《基於Quartus II的FPGA/CPLD設計與實踐》是2010年4月出版的一本書,適合從事FPGA/CPLD研發的技術人員閱讀,也可作為高等學校相關專業的教學用書。...

基於Quartus II的FPGA/CPLD數字系統設計實例編輯 鎖定 基於Quartus II的FPGA/CPLD數字系統設計實例於2013年出版 書名 基於Quartus II的FPGA/CPLD數字系統設計實例 ...

《基於Quartus II的FPGA/CPLD設計實例精解》以實例精解的方式講述基於Quaitus II的FPGA/CPLD設計方法和技巧,主要包括EDA與可程式器件概述Quarts II開發環境、硬體設計...

本書是介紹用QuartusⅡ6.0進行計算機設計的教材。書中以最新的手法設計了一種抗...1. 基於Quartus II的計算機核心設計 .豆瓣[引用日期2019-03-14] 詞條...

《基於Quartus II的計算機組成與體系結構綜合實驗教程》一書的出版社是科學,作者是楊軍,出版時間是2011-1。...

《EDA技術與套用—基於QuartusII和VHDL》是2012年北京航空航天大學出版社出版的圖書,作者是劉昌華。...

《基於VHDL與QuartusII軟體的可程式邏輯器件套用與開發》是2011年國防工業出版社出版的圖書,作者是鄭燕,赫建國。...

本書的主要內容包括:可程式邏輯器件結構、Altera 公司最新系列器件的性能特點、VHDL語言、Altera公司新一代的PLD開發軟體Quartus II使用入門與進階、第三方工具軟體、...

《基於VHDL語言與QuartusII軟體的可程式邏輯器件套用與開發》是2007年國防工業出版社出版的圖書,作者是鄭燕。...

《MAX+plusII和QuartusII套用與開發技巧》是2007年機械工業出版社出版的圖書,作者是王輝等。...

《基於Quartus2的FPGA (平裝)》是2006年電子工業出版社出版的圖書,作者是李洪偉。...... 本書介紹了Altera公司推出的Quartus II 4.0的使用方法和設計技巧。Altera公...

《基於Quartus II的CPLD的數字系統設計與實現》是機械工業出版社於2012年出版的圖書,作者是王忠林。...

《 MAX+plisII和QuartusII套用與開發技巧》是2007年機械工業出版社出版的圖書,作者是王輝。...

MAX+PLUSII:普遍認為MaxplusII曾經是最優秀的PLD開發平台之一,適合開發早期的中小規模PLD/FPGA由QuartusII替代,不再推薦使用。QuartusII:Altera新一代FPGA/PLD開發...

在介紹FPGA/CPLD概念的基礎上,介紹了Altera主流FPGA/CPLD的結構與特點,並通過豐富的實例講解Quartus II與ModelSim、Synplify Pro等常用EDA工具的開發流程。...