起源

達靈頓結構是由

貝爾實驗室的工程師悉尼·達靈頓(Sidney Darlington)在1953年發明的。他後來將這種兩三個晶體接在一起、共同接在一個集電極的創意申報了專利。

另一種看起來與之相似的結構是將兩個半導體類型電晶體連線起來(例如NPN-PNP),這種結構被稱作是西克對管(Sziklai pair)。

特性

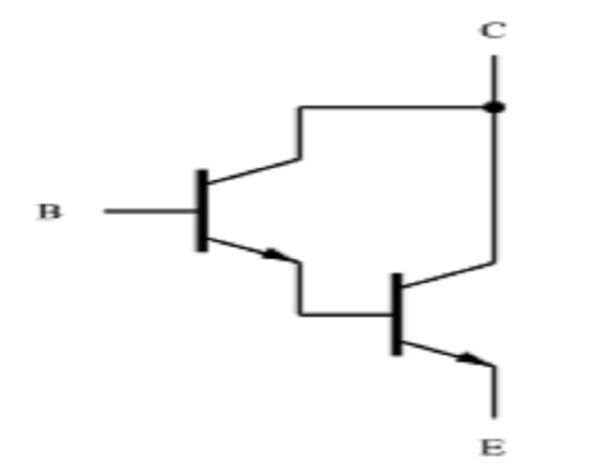

一個達靈頓電晶體看起來就像是具有很高電流增益(大約是所使用的兩個雙極性電晶體的電流增益的乘積)的雙極性電晶體。事實上,整個積體電路具有三個引腳(B-基極,C-集電極,E-發射極),這些概念都可以通過標準電晶體的類似概念進行理解。

複合結構的電流增益

和兩個單一電晶體的電流增益

之間的關係可以表示為:

如果β1和β2足夠高(達到上百),那么以上關係可以簡化為:

現在,達靈頓電晶體產品的典型電流增益可以達到1000甚至更高,因此只需要很小的基極電流就可以讓電晶體導通。然而,這樣高的電流增益也帶來了一些缺點。

缺點

達靈頓電晶體的一個缺點是它的基極-發射極電壓被加倍了。由於整個達靈頓結構的基極和發射極之間有兩個結,因此等效的基極-發射極電壓是各個電晶體的基極-發射極電壓之和:

對於矽半導體電晶體,當其處於工作區或飽和狀態,其基極-發射極電壓VBEi大約為0.65伏特,因此它們組成的達靈頓電晶體結構總的基極-發射極電壓大約就是1.3伏特。

達靈頓電晶體的另外一個缺點是其飽和電壓更大。輸出級電晶體不能飽和(也就是說其基極-集電極的結必須維持反向偏置),因為當第一級電晶體處於飽和狀態時,它將在輸出級電晶體的集電極和基極之間施加滿幅負反饋。由於輸出級電晶體的集電極-發射極電壓等於其自身基極-發射極電壓和前一級電晶體的集電極-發射極電壓之和,兩個電壓在正常工作狀態時都具有正數值,因此它總是超過了基極-發射極電壓,即總有

所以,達靈頓電晶體的飽和電壓是一個基極-發射極電壓(矽管的情況大約是0.65伏特),比電晶體本身的飽和電壓(約0.1到0.2伏特之間)要大得多。假設都具有相等的集電極電流,這個缺點會表現為達靈頓電晶體的耗散功率比單一電晶體要大。此外,更高的集電極-發射極電壓在

電晶體-電晶體邏輯電路(Transistor-transistor logic, TTL)電路中可能會引起邏輯錯誤。

達靈頓結構導致的另一個問題是,其開關速度不得不降低,因為第一級電晶體不能夠主動抑制第二級電晶體的基極電流,因此開關回響比單一的電晶體更慢。為了緩解這一缺點,第二級電晶體的基極和發射極之間常常會連線一個幾百

歐姆的電阻。這個電阻在基極和發射極之間為積累在基極-發射極結上的電荷提供了一條阻抗較低的釋放路徑,由此使得達靈頓電晶體的開關速度更快。

在高頻率的情況里,達靈頓對將具有比單一電晶體更大的相位移動,因此它在負反饋的情況下會變得不穩定。

達靈頓電晶體常把兩個分立的電晶體做成集成晶片的形式。在上圖中,左邊的電晶體Q

1可以是低功率類型的,右邊的Q

2則需要高功率類型的。整個達靈頓結構的最大集電極電流I

C(max)大約等於Q

2的集電極電流。2N6282是一種典型的達靈頓結構集成晶片,內部包含了一個上文提到過的關斷電阻,在I

C等於10

安培時具有2400的電流增益。

實際上,達靈頓結構可以對安全電壓以下皮膚產生的接觸電流進行足夠敏感的回響,因此它常被用來構成觸控開關的信號輸入級。