暫存器檔案(register file)又稱暫存器堆,是CPU中多個暫存器組成的陣列,通常由快速的靜態隨機讀寫存儲器(SRAM)實現。這種RAM具有專門的讀連線埠與寫連線埠,可以多路並發訪問不同的暫存器。

CPU的指令集架構總是定義了一批暫存器,用於在記憶體與CPU運算部件之間暫存數據。在更為簡化的CPU,這些架構暫存器(architectural registers)一一對應與CPU內的物理存在的暫存器。在更為複雜的CPU,使用暫存器重命名技術,使得執行期間哪個架構暫存器對應於哪個暫存器堆的物理存儲條目(physical entry stores)是動態改變的。暫存器堆是指令集架構的一部分,程式可以訪問,這與透明的CPU高速快取(cache)不同。

基本介紹

- 中文名:暫存器檔案

- 外文名:register file

- 又稱:暫存器堆

實現

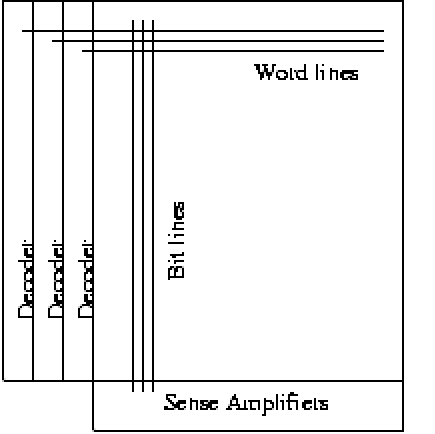

一個典型的暫存器堆

一個典型的暫存器堆解碼

- 解碼器經常劃分為預解碼(predecoder)與解碼(decoder)。

- 解碼器是一系列的與門,最終選定並驅動字線。

- 每個讀連線埠與寫連線埠都有自己的專用解碼器。例如,如果陣列有4個讀連線埠與2個寫連線埠,那么就有6套地址解碼器,每個暫存器堆的條目有6條字線。

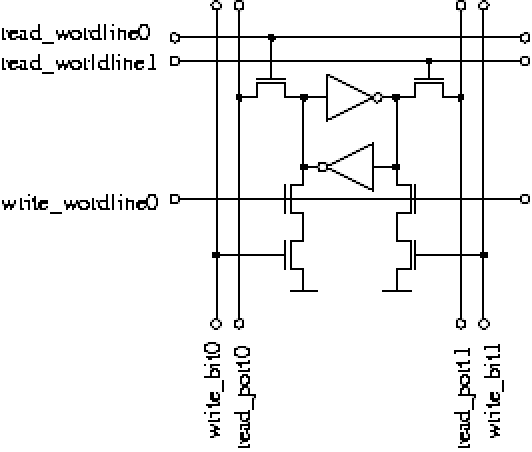

陣列

- 狀態被存儲在一對反相器中;

- 數據通過一個NMOS電晶體取到與字線相配的“讀位線”上。

- 數據通過“寫位線”的電位來控制2個作為開關的NMOS管導通或者截止,從而把反相器的一端或者另外一端接地來寫入數據。

- 因此:讀連線埠需要一個電晶體,而寫連線埠需要4個電晶體!

- 在基本存儲單元之間共享線路,如Vdd與Vss電源線。

- 讀位線經常預充為Vdd或者Vss。

- 讀位線經常是在Vdd或Vss電位附近的一個小幅值內波動來表示存儲的狀態。由感知放大器把這種小幅值信號變換為全幅值的邏輯信號。小幅值信號的速度更快,因為位線僅有很小的驅動但是具有很大的寄生電容。

- 寫位線是全幅值信號,這可能會導致與它伴生走線的讀位線的很大幹擾。

- 如果Vdd是平行走線可以關閉,如果這個周期內一個寫連線埠正在寫入。這種最佳化提高了寫速度。

- 採用低功率電子設備來降低能耗