基本介紹

- 中文名:多核技術

- 套用:處理器

- 解決問題:降低處理器熱量

- 解決策略:“分治法”戰略

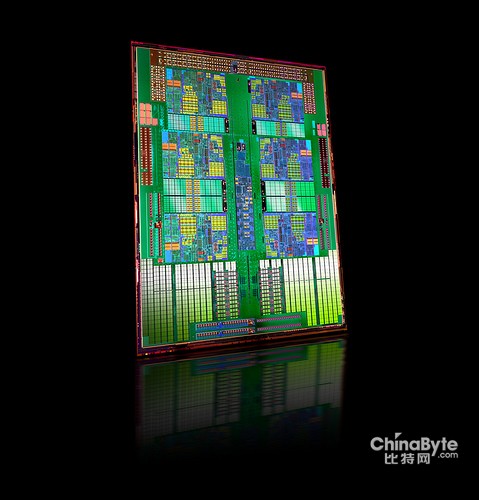

多核心是指在一枚處理器中集成兩個或多個完整的計算引擎(核心)。多核技術的開發源於工程師們認識到,僅提高單核晶片的速度會產生過多熱量且無法帶來相應的性能改善...

多核處理器是指在一枚處理器中集成兩個或多個完整的計算引擎(核心),此時處理器能支持系統匯流排上的多個處理器,由匯流排控制器提供所有匯流排控制信號和命令信號。多核...

《多核多執行緒技術》是2011年1月上海交通大學出版社出版的圖書,作者是英特爾亞太研發有限公司、英特爾軟體學院教材編寫組。...

《多核程式設計技術》是2007年電子工業出版社出版的圖書,作者是阿克特等。...... 本書從原理、技術、經驗和工具等方面為讀者提供關於多核程式設計技術的全方位理解...

隨著技術的成熟,當多核為伺服器帶來足夠的性能提升以及更具競爭力的價格的時候,多核,更像是為x86架構與RISC架構的競爭提供了一個舞台,不僅是致力於x86伺服器的...

《多核程式設計技術--通過軟體多執行緒提升性能》是2007年電子工業出版社出版的一本圖書,作者是Shameem Akhter 。...

《多核程式設計》是2007年清華大學出版社出版的圖書,作者是多核系列教材編寫組。該書主要以介紹多核體系結構、多核處理器、硬體支持、系統軟體的現狀,詳細講解了在...

AMD多核處理技術多核解決方案 編輯 多核處理能夠幫助應對這些挑戰。利用單一晶片上兩個或更多處理器的處理能力,AMD真正的多核處理器能夠提供行業領先的性能和獨一...

多核心cpu主要分原生多核和封裝多核。原生多核指的是真正意義上的多核,最早由AMD提出,每個核心之間都是完全獨立的,都擁有自己的前端匯流排,不會造成衝突,即使在高...

《TI—DSP多核技術及實時軟體開發》是2015年電子工業出版社出版的圖書,作者是潘曄、廖昌俊。...

多核心(multicore chips)是指在一枚處理器(chip)中集成兩個或多個完整的計算引擎(核心)。多核技術的開發源於工程師們認識到,僅僅提高單核晶片(one chip)的速度...

多核心編程是一個現在的程式設計師必須去了解的技術,和原來的單核技術不一樣,多核編程更講究程式的架構,任務的分配,每個處理機的負載。我們現在用的多核編程工具注意...

AMD的雙核技術它並不只是簡單地將兩個Opteron處理器核心集成在一個矽晶片(Die)上,與單核Opteron相比,它增添了“系統請求接口”(System Request Interface,SRI)和“...

《多核套用架構關鍵技術:軟體管道與SOA》是2010年機械工業出版社出版的圖書,作者是艾薩克遜。...

《多核套用架構關鍵技術——軟體管道與SOA》是2010年6月1日機械工業出版社出版的圖書,作者是(美)區薩克遜。...

《多核計算與程式設計》作者是周偉明,由華中科技大學出版社於2009年正式出版,定價88元。主要介紹適應於多核(或多處理器)計算機系統的算法和程式,共分為:基礎知識...

同時運行多個工作執行緒的技術,和CMP(Chip MultiProcessing,晶片多處理)不同,後者是通過集成多個處理核心的方式來讓系統的處理能力提升——也就是現在常見的多核技術...

從8086到80186、80286、80386、80486,再到後來的奔騰系列以及現在的多核技術,都是使用一脈相承的x86指令集,既不斷擴展又向後兼容。...

多核X4筆記本散熱器屬於九州風神的一個全新的產品系列。...... 全球領先多核調控技術(M.C.C.T),4級調節可供選擇,可根據本本發熱部位及功耗隨意調控各風扇開關。...

要在整個行業中實現多核處理性能,就必須滿足製程技術和多核心處理器製造能力(矽核尺寸必須滿足批量生產的要求)兩方面的要求。英特爾具有雄厚的實力,可以滿足這兩個...

多核技術能夠使伺服器並行處理任務,而在以前,這可能需要使用多個處理器,多核系統更易於擴充,並且能夠在更纖巧的外形中融入更強大的處理性能,這種外形所用的功耗更...

面向台式機的英特爾 酷睿™2 四核處理器採用強大的多核技術,能有效處理密集計算和虛擬化工作負載。最新型英特爾酷睿2 四核處理器基於 45 納米英特爾酷睿™ 微...